The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

32

# SH7619 Group

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>TM</sup> RISC engine Family / SH7619 Series SH7619 R4S76190

Hardware Manua

Rev.5.00

Revision Date: Mar. 15, 2007

Renesas Technology www.renesas.com

#### Notes regarding these materials

- 1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to quard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document. Renesas semiconductor products, or if you have any other inquiries.

#### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

#### **Preface**

The SH7619 Group RISC (Reduced Instruction Set Computer) microcomputers include a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using the SH/7619 in the design of

application systems. Target users are expected to understand the fundamentals of

electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of the SH/7619 to the target users.

Refer to the SH-1/SH-2/SH-DSP Software Manual for a detailed description of the

instruction set.

Notes on reading this manual:

In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-1/SH-2/SH-DSP Software Manual.

• In order to understand the details of a register when its name is known

The addresses, bits, and initial values of the registers are summarized in section 23, List of Registers.

Examples: Register name: The following notation is used for cases when the same or a

similar function, e.g. 16-bit timer pulse unit or serial communication interface, is implemented on more than one

channel:

XXX\_N (XXX is the register name and N is the channel

number)

Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal: XXXX

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/

## SH/7619 Group manuals:

| Document Title                   | Document No. |

|----------------------------------|--------------|

| SH/7619 Group Hardware Manual    | This manual  |

| SH-1/SH-2/SH-DSP Software Manual | REJ09B0171   |

## User's manuals for development tools:

| Document Title                                                                                     | Document No. |

|----------------------------------------------------------------------------------------------------|--------------|

| SuperH <sup>™</sup> RISC engine C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10B0152   |

| SuperH RISC engine High-performance Embedded Workshop 3 User's Manual                              | REJ10B0025   |

| SuperH RISC engine High-performance Embedded Workshop 3 Tutorial                                   | REJ10B0023   |

## Application note:

| Document Title                    | Document No. |

|-----------------------------------|--------------|

| SuperH RISC engine C/C++ Compiler | REJ05B0463   |

# Contents

| Secti | on 1 Ove                 | erview                          | 1  |

|-------|--------------------------|---------------------------------|----|

| 1.1   | Features.                |                                 | 2  |

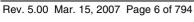

| 1.2   | Block Di                 | agram                           | 7  |

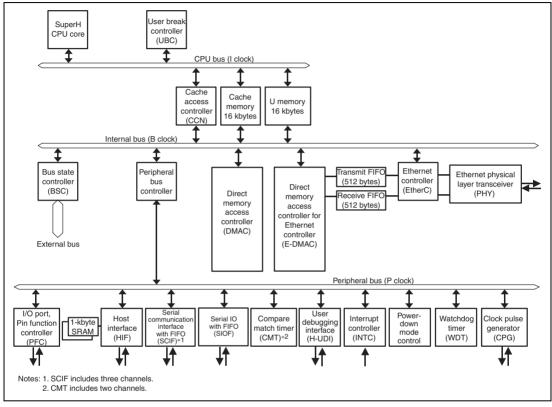

| 1.3   | Pin Assig                | gnments                         | 8  |

| 1.4   | Pin Func                 | tions                           | 9  |

|       |                          |                                 |    |

| Secti |                          | J                               |    |

| 2.1   |                          |                                 |    |

| 2.2   | •                        | Configuration                   |    |

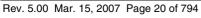

|       | 2.2.1                    | General Registers (Rn)          |    |

|       | 2.2.2                    | Control Registers               |    |

|       | 2.2.3                    | System Registers                |    |

|       | 2.2.4                    | Initial Values of Registers     |    |

| 2.3   | Data For                 | mats                            |    |

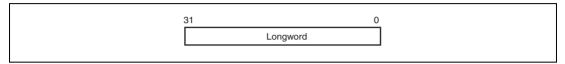

|       | 2.3.1                    | Register Data Format            |    |

|       | 2.3.2                    | Memory Data Formats             |    |

|       | 2.3.3                    | Immediate Data Formats          | 29 |

| 2.4   | Features of Instructions |                                 |    |

|       | 2.4.1                    | RISC Type                       |    |

|       | 2.4.2                    | Addressing Modes                |    |

|       | 2.4.3                    | Instruction Formats             | 35 |

| 2.5   | Instruction              | on Set                          | 39 |

|       | 2.5.1                    | Instruction Set by Type         | 39 |

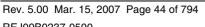

| 2.6   | Processir                | ng States                       | 51 |

|       | 2.6.1                    | State Transition                | 51 |

| Sacti | on 3 Cac                 | he                              | 53 |

| 3.1   |                          | nc                              |    |

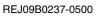

| 3.1   | 3.1.1                    | Cache Structure                 |    |

|       | 3.1.2                    | Divided Areas and Cache         |    |

| 3.2   | U.1.2                    | Descriptions                    |    |

| 3.2   | 3.2.1                    | Cache Control Register 1 (CCR1) |    |

| 3.3   |                          | n                               |    |

| ر.ر   | 3.3.1                    | Searching Cache                 |    |

|       | 3.3.2                    | Read Access                     |    |

|       | 3.3.3                    | Write Access                    |    |

|       | 5.5.5                    | WITHE ACCESS                    | 59 |

|      | 3.3.4    | Write-Back Buffer                                                      | 59 |

|------|----------|------------------------------------------------------------------------|----|

|      | 3.3.5    | Coherency of Cache and External Memory                                 | 59 |

| 3.4  | Memor    | y-Mapped Cache                                                         | 60 |

|      | 3.4.1    | Address Array                                                          | 60 |

|      | 3.4.2    | Data Array                                                             | 61 |

|      | 3.4.3    | Usage Examples                                                         |    |

| Sect | ion 4 U  | Memory                                                                 | 65 |

| 4.1  |          | S                                                                      |    |

| 4.2  | Usage l  | Notes                                                                  | 65 |

| Sect | ion 5 Ex | ception Handling                                                       | 67 |

| 5.1  |          | 2W                                                                     |    |

|      | 5.1.1    | Types of Exception Handling and Priority                               | 67 |

|      | 5.1.2    | Exception Handling Operations                                          |    |

|      | 5.1.3    | Exception Handling Vector Table                                        |    |

| 5.2  | Resets.  |                                                                        | 71 |

|      | 5.2.1    | Types of Resets                                                        | 71 |

|      | 5.2.2    | Power-On Reset                                                         | 71 |

|      | 5.2.3    | H-UDI Reset                                                            | 72 |

| 5.3  | Addres   | s Errors                                                               | 73 |

|      | 5.3.1    | Address Error Sources                                                  | 73 |

|      | 5.3.2    | Address Error Exception Source                                         | 73 |

| 5.4  | Interrup | ots                                                                    | 74 |

|      | 5.4.1    | Interrupt Sources                                                      | 74 |

|      | 5.4.2    | Interrupt Priority                                                     | 75 |

|      | 5.4.3    | Interrupt Exception Handling                                           | 75 |

| 5.5  | Excepti  | ons Triggered by Instructions                                          | 76 |

|      | 5.5.1    | Types of Exceptions Triggered by Instructions                          | 76 |

|      | 5.5.2    | Trap Instructions                                                      | 76 |

|      | 5.5.3    | Illegal Slot Instructions                                              | 77 |

|      | 5.5.4    | General Illegal Instructions                                           | 77 |

| 5.6  | Cases v  | when Exceptions are Accepted                                           | 78 |

| 5.7  | Stack S  | tates after Exception Handling Ends                                    | 79 |

| 5.8  | Usage l  | Notes                                                                  | 81 |

|      | 5.8.1    | Value of Stack Pointer (SP)                                            | 81 |

|      | 5.8.2    | Value of Vector Base Register (VBR)                                    |    |

|      | 5.8.3    | Address Errors Caused by Stacking for Address Error Exception Handling | 81 |

|      | 5.8.4    | Notes on Slot Illegal Instruction Exception Handling                   | 81 |

| Secti | on 6 Inte | errupt Controller (INTC)                                                 | 83  |

|-------|-----------|--------------------------------------------------------------------------|-----|

| 6.1   |           | -                                                                        |     |

| 6.2   | Input/Ou  | tput Pins                                                                | 85  |

| 6.3   | Register  | Descriptions                                                             | 85  |

|       | 6.3.1     | Interrupt Control Register 0 (ICR0)                                      | 86  |

|       | 6.3.2     | IRQ Control Register (IRQCR)                                             | 87  |

|       | 6.3.3     | IRQ Status register (IRQSR)                                              | 90  |

|       | 6.3.4     | Interrupt Priority Registers A to G (IPRA to IPRG)                       | 95  |

| 6.4   | Interrupt | Sources                                                                  | 97  |

|       | 6.4.1     | External Interrupts                                                      | 97  |

|       | 6.4.2     | On-Chip Peripheral Module Interrupts                                     | 99  |

|       | 6.4.3     | User Break Interrupt                                                     | 99  |

|       | 6.4.4     | H-UDI Interrupt                                                          | 99  |

| 6.5   | Interrupt | Exception Handling Vector Table                                          | 100 |

| 6.6   | Interrupt | Operation                                                                | 102 |

|       | 6.6.1     | Interrupt Sequence                                                       | 102 |

|       | 6.6.2     | Stack after Interrupt Exception Handling                                 | 104 |

| 6.7   | Interrupt | Response Time                                                            | 104 |

|       |           |                                                                          |     |

|       |           | S State Controller (BSC)                                                 |     |

| 7.1   |           |                                                                          |     |

| 7.2   | -         | tput Pins                                                                |     |

| 7.3   |           | erview                                                                   |     |

|       | 7.3.1     | Area Division                                                            |     |

|       | 7.3.2     | Shadow Area                                                              | 112 |

|       | 7.3.3     | Address Map                                                              |     |

|       | 7.3.4     | Area 0 Memory Type and Memory Bus Width                                  |     |

|       | 7.3.5     | Data Alignment                                                           |     |

| 7.4   | Register  | Descriptions                                                             |     |

|       | 7.4.1     | Common Control Register (CMNCR)                                          |     |

|       | 7.4.2     | CSn Space Bus Control Register (CSnBCR) $(n = 0, 2, 3, 4, 5B, 6B) \dots$ |     |

|       | 7.4.3     | CSn Space Wait Control Register (CSnWCR) (n = 0, 3, 4, 5B, 6B)           |     |

|       | 7.4.4     | SDRAM Control Register (SDCR)                                            |     |

|       | 7.4.5     | Refresh Timer Control/Status Register (RTCSR)                            |     |

|       | 7.4.6     | Refresh Timer Counter (RTCNT)                                            |     |

|       | 7.4.7     | Refresh Time Constant Register (RTCOR)                                   |     |

| 7.5   | -         | n                                                                        |     |

|       | 7.5.1     | Endian/Access Size and Data Alignment                                    |     |

|       | 7.5.2     | Normal Space Interface                                                   |     |

|       | 7.5.3     | Access Wait Control                                                      | 154 |

|       | 7.5.4   | Extension of Chip Select (CSn) Assertion Period | 156 |

|-------|---------|-------------------------------------------------|-----|

|       | 7.5.5   | SDRAM Interface                                 |     |

|       | 7.5.6   | Byte-Selection SRAM Interface                   | 186 |

|       | 7.5.7   | PCMCIA Interface                                | 191 |

|       | 7.5.8   | Wait between Access Cycles                      | 198 |

|       | 7.5.9   | Others                                          | 198 |

| Secti | on 8 Cl | ock Pulse Generator (CPG)                       | 201 |

| 8.1   |         | ·S                                              |     |

| 8.2   | Input/C | Output Pins                                     | 204 |

| 8.3   | Clock ( | Operating Modes                                 | 204 |

| 8.4   | Registe | r Descriptions                                  | 206 |

|       | 8.4.1   | Frequency Control Register (FRQCR)              | 206 |

|       | 8.4.2   | PHY Clock Frequency Control Register (MCLKCR)   | 208 |

|       | 8.4.3   | Usage Notes                                     | 209 |

| 8.5   | Changi  | ng Frequency                                    | 210 |

|       | 8.5.1   | Changing Multiplication Ratio                   | 210 |

|       | 8.5.2   | Changing Division Ratio                         | 211 |

|       | 8.5.3   | Changing Clock Operating Mode                   | 211 |

| 8.6   | Notes o | on Board Design                                 | 213 |

| Secti | on 9 W  | atchdog Timer (WDT)                             | 215 |

| 9.1   | Feature | ·s                                              | 215 |

| 9.2   | Registe | r Descriptions                                  | 217 |

|       | 9.2.1   | Watchdog Timer Counter (WTCNT)                  | 217 |

|       | 9.2.2   | Watchdog Timer Control/Status Register (WTCSR)  | 217 |

|       | 9.2.3   | Notes on Register Access                        | 219 |

| 9.3   | WDT C   | Operation                                       | 220 |

|       | 9.3.1   | Canceling Software Standbys                     | 220 |

|       | 9.3.2   | Changing Frequency                              | 221 |

|       | 9.3.3   | Using Watchdog Timer Mode                       | 221 |

|       | 9.3.4   | Using Interval Timer Mode                       | 222 |

| 9.4   | Usage l | Notes                                           | 222 |

| Secti | on 10 P | Power-Down Modes                                | 223 |

| 10.1  | Feature | s                                               | 223 |

|       | 10.1.1  | Types of Power-Down Modes                       | 223 |

| 10.2  | Input/O | Output Pins                                     | 224 |

| 10.3  | Registe | r Descriptions                                  | 224 |

|       | 10 3 1  | Standby Control Register (STBCR)                | 225 |

|       | 10.3.2    | Standby Control Register 2 (STBCR2)                 | 226 |

|-------|-----------|-----------------------------------------------------|-----|

|       | 10.3.3    | Standby Control Register 3 (STBCR3)                 | 227 |

|       | 10.3.4    | Standby Control Register 4 (STBCR4)                 | 228 |

| 10.4  | Sleep M   | ode                                                 | 229 |

|       | 10.4.1    | Transition to Sleep Mode                            | 229 |

|       | 10.4.2    | Canceling Sleep Mode                                | 229 |

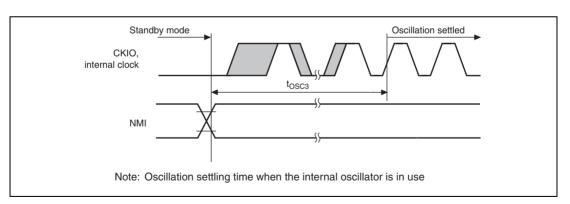

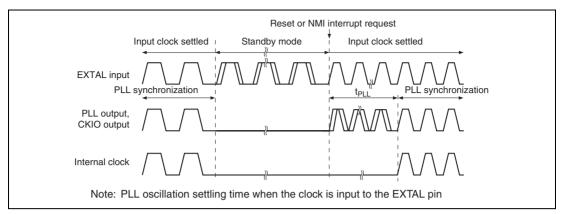

| 10.5  | Software  | e Standby Mode                                      | 230 |

|       | 10.5.1    | Transition to Software Standby Mode                 | 230 |

|       | 10.5.2    | Canceling Software Standby Mode                     | 231 |

| 10.6  | Module    | Standby Mode                                        | 232 |

|       | 10.6.1    | Transition to Module Standby Mode                   | 232 |

|       | 10.6.2    | Canceling Module Standby Function                   | 232 |

| Secti | on 11 Et  | thernet Controller (EtherC)                         | 233 |

| 11.1  |           |                                                     |     |

| 11.2  | Input/Ou  | utput Pins                                          | 235 |

| 11.3  | Register  | Description                                         | 237 |

|       | 11.3.1    | EtherC Mode Register (ECMR)                         |     |

|       | 11.3.2    | EtherC Status Register (ECSR)                       | 241 |

|       | 11.3.3    | EtherC Interrupt Permission Register (ECSIPR)       | 243 |

|       | 11.3.4    | PHY Interface Register (PIR)                        | 244 |

|       | 11.3.5    | MAC Address High Register (MAHR)                    | 245 |

|       | 11.3.6    | MAC Address Low Register (MALR)                     | 245 |

|       | 11.3.7    | Receive Frame Length Register (RFLR)                | 246 |

|       | 11.3.8    | PHY Status Register (PSR)                           | 247 |

|       | 11.3.9    | Transmit Retry Over Counter Register (TROCR)        |     |

|       | 11.3.10   | Delayed Collision Detect Counter Register (CDCR)    | 248 |

|       | 11.3.11   | Lost Carrier Counter Register (LCCR)                |     |

|       | 11.3.12   | Carrier Not Detect Counter Register (CNDCR)         | 248 |

|       | 11.3.13   | CRC Error Frame Counter Register (CEFCR)            | 249 |

|       | 11.3.14   | Frame Receive Error Counter Register (FRECR)        | 249 |

|       | 11.3.15   | Too-Short Frame Receive Counter Register (TSFRCR)   | 249 |

|       | 11.3.16   | Too-Long Frame Receive Counter Register (TLFRCR)    | 250 |

|       | 11.3.17   | Residual-Bit Frame Counter Register (RFCR)          | 250 |

|       | 11.3.18   | Multicast Address Frame Counter Register (MAFCR)    | 250 |

|       | 11.3.19   | IPG Register (IPGR)                                 | 251 |

|       | 11.3.20   | Automatic PAUSE Frame Set Register (APR)            | 251 |

|       | 11.3.21   | Manual PAUSE Frame Set Register (MPR)               | 252 |

|       | 11.3.22   | PAUSE Frame Retransfer Count Set Register (TPAUSER) |     |

| 114   | Operation | - ·                                                 | 253 |

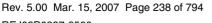

|       | 11.4.1   | Transmission                                                | 253 |

|-------|----------|-------------------------------------------------------------|-----|

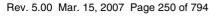

|       | 11.4.2   | Reception                                                   | 255 |

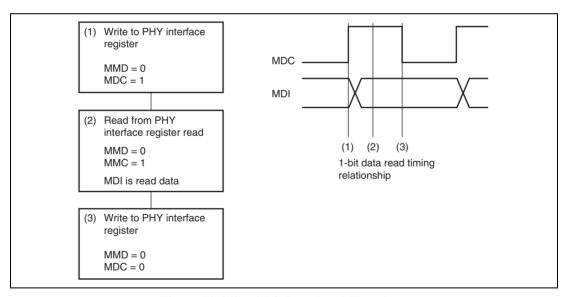

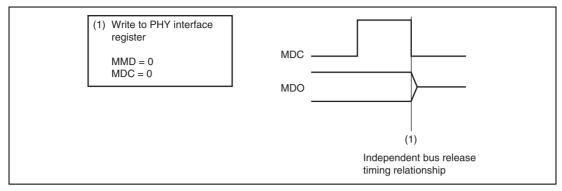

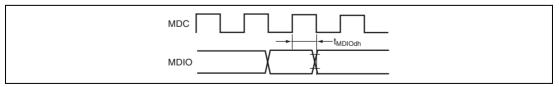

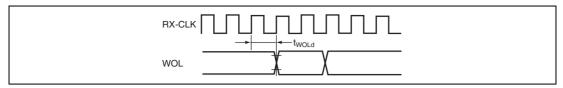

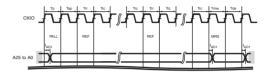

|       | 11.4.3   | MII Frame Timing                                            | 256 |

|       | 11.4.4   | Accessing MII Registers                                     | 258 |

|       | 11.4.5   | Magic Packet Detection                                      | 261 |

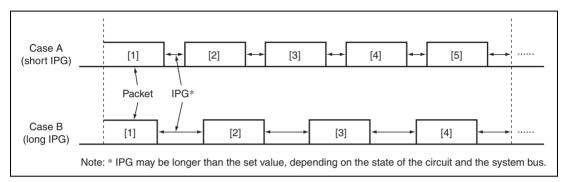

|       | 11.4.6   | Operation by IPG Setting                                    | 262 |

|       | 11.4.7   | Flow Control                                                | 262 |

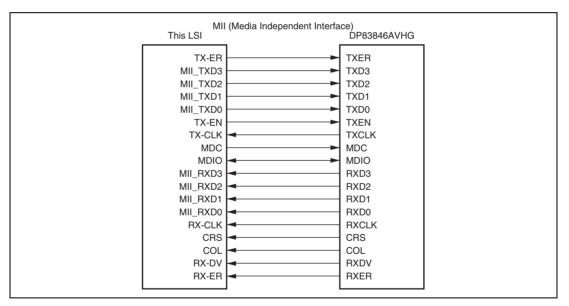

| 11.5  | Connect  | ion to PHY-LSI                                              | 263 |

| 11.6  | Usage N  | otes                                                        | 264 |

|       |          |                                                             |     |

| Secti |          | chernet Controller Direct Memory Access Controller          | 265 |

|       | `        | E-DMAC)                                                     |     |

| 12.1  |          |                                                             |     |

| 12.2  | Ū        | Descriptions                                                |     |

|       | 12.2.1   | E-DMAC Mode Register (EDMR)                                 |     |

|       | 12.2.2   | E-DMAC Transmit Request Register (EDTRR)                    |     |

|       | 12.2.3   | E-DMAC Receive Request Register (EDRRR)                     |     |

|       | 12.2.4   | Transmit Descriptor List Address Register (TDLAR)           |     |

|       | 12.2.5   | Receive Descriptor List Address Register (RDLAR)            |     |

|       | 12.2.6   | EtherC/E-DMAC Status Register (EESR)                        |     |

|       | 12.2.7   | EtherC/E-DMAC Status Interrupt Permission Register (EESIPR) |     |

|       | 12.2.8   | Transmit/Receive Status Copy Enable Register (TRSCER)       | 279 |

|       | 12.2.9   | Receive Missed-Frame Counter Register (RMFCR)               |     |

|       | 12.2.10  | Transmit FIFO Threshold Register (TFTR)                     | 282 |

|       | 12.2.11  | FIFO Depth Register (FDR)                                   | 283 |

|       | 12.2.12  | Receiving Method Control Register (RMCR)                    | 284 |

|       | 12.2.13  | E-DMAC Operation Control Register (EDOCR)                   | 285 |

|       | 12.2.14  | Receiving-Buffer Write Address Register (RBWAR)             | 286 |

|       | 12.2.15  | Receiving-Descriptor Fetch Address Register (RDFAR)         | 286 |

|       | 12.2.16  | Transmission-Buffer Read Address Register (TBRAR)           | 286 |

|       | 12.2.17  | Transmission-Descriptor Fetch Address Register (TDFAR)      | 287 |

|       | 12.2.18  | Flow Control FIFO Threshold Register (FCFTR)                | 287 |

|       | 12.2.19  | Transmit Interrupt Register (TRIMD)                         |     |

| 12.3  | Operatio | on                                                          |     |

|       | 12.3.1   | Descriptor List and Data Buffers                            |     |

|       | 12.3.2   | Transmission                                                |     |

|       | 12.3.3   | Reception                                                   |     |

|       | 12.3.4   | Multi-Buffer Frame Transmit/Receive Processing              |     |

| 12.4  | Usage N   | lotes                                                          | 304 |

|-------|-----------|----------------------------------------------------------------|-----|

|       | 12.4.1    | Usage Notes on SH-Ether EtherC/E-DMAC Status Register (EESR)   | 304 |

|       | 12.4.2    | Usage Notes on SH-Ether Transmit-FIFO Underflow                | 313 |

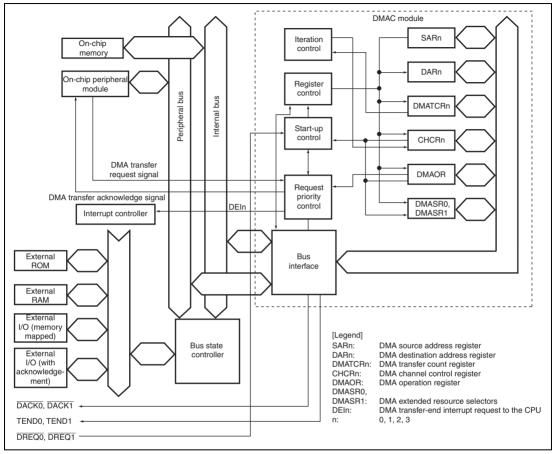

| Secti | on 13 D   | irect Memory Access Controller (DMAC)                          | 323 |

| 13.1  | Features  | · · · · · · · · · · · · · · · · · · ·                          | 323 |

| 13.2  | Input/O   | utput Pins                                                     | 325 |

| 13.3  | Register  | Descriptions                                                   | 326 |

|       | 13.3.1    | DMA Source Address Registers 0 to 3 (SAR_0 to SAR_3)           | 327 |

|       | 13.3.2    | DMA Destination Address Registers 0 to 3 (DAR_0 to DAR_3)      | 327 |

|       | 13.3.3    | DMA Transfer Count Registers 0 to 3 (DMATCR_0 to DMATCR_3)     | 327 |

|       | 13.3.4    | DMA Channel Control Registers 0 to 3 (CHCR_0 to CHCR_3)        | 328 |

|       | 13.3.5    | DMA Operation Register (DMAOR)                                 | 333 |

|       | 13.3.6    | DMA Extended Resource Selectors 0 and 1 (DMARS0 and DMARS1)    | 335 |

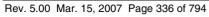

| 13.4  | Operation | on                                                             | 337 |

|       | 13.4.1    | DMA Transfer Flow                                              | 337 |

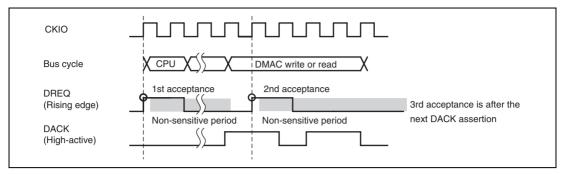

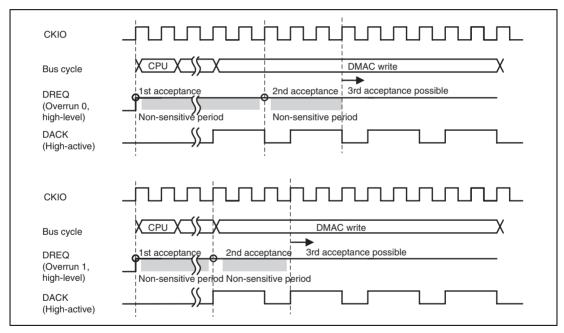

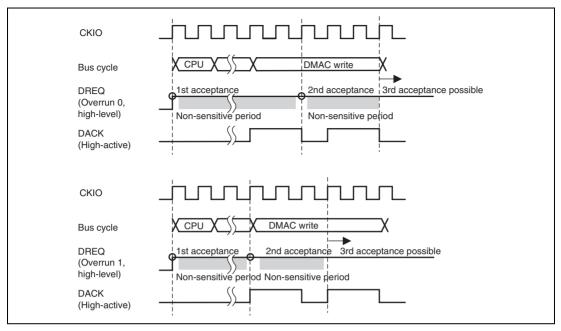

|       | 13.4.2    | DMA Transfer Requests                                          | 339 |

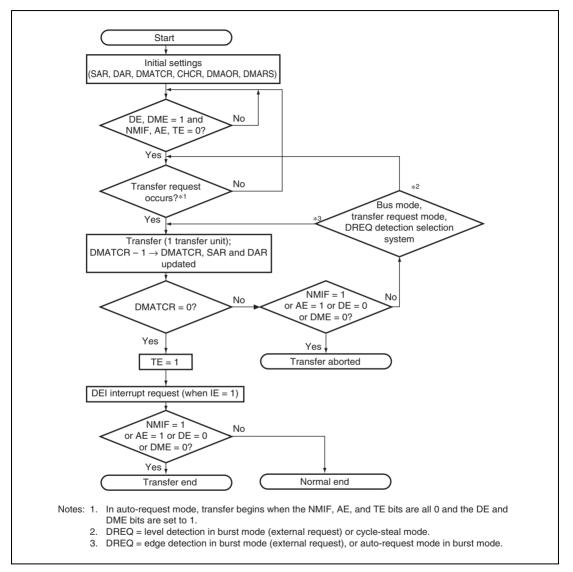

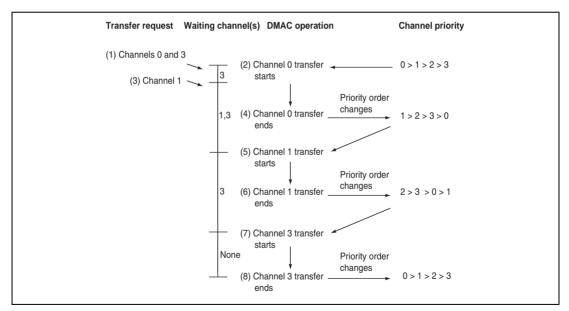

|       | 13.4.3    | Channel Priority                                               | 341 |

|       | 13.4.4    | DMA Transfer Types                                             |     |

|       | 13.4.5    | Number of Bus Cycle States and DREQ Pin Sampling Timing        | 353 |

| 13.5  | _         | lotes                                                          |     |

|       | 13.5.1    | Notes on DACK Pin Output                                       |     |

|       | 13.5.2    | Notes On DREQ Sampling When DACK is Divided in External Access | 358 |

|       | 13.5.3    | Other Notes                                                    | 361 |

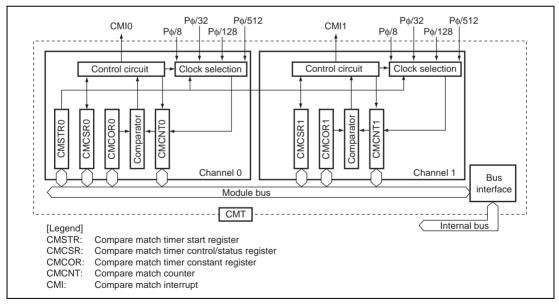

| Secti | on 14 C   | ompare Match Timer (CMT)                                       | 363 |

| 14.1  |           | *                                                              |     |

| 14.2  | Register  | Descriptions                                                   | 364 |

|       | 14.2.1    | Compare Match Timer Start Register (CMSTR)                     | 364 |

|       | 14.2.2    | Compare Match Timer Control/Status Register (CMCSR)            | 365 |

|       | 14.2.3    | Compare Match Counter (CMCNT)                                  |     |

|       | 14.2.4    | Compare Match Constant Register (CMCOR)                        | 366 |

| 14.3  | Operation | on                                                             | 367 |

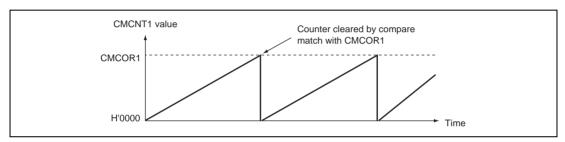

|       | 14.3.1    | Interval Count Operation                                       | 367 |

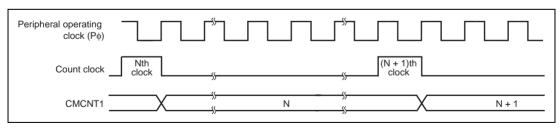

|       | 14.3.2    | CMCNT Count Timing                                             | 367 |

| 14.4  | Interrup  | ts                                                             | 368 |

|       | 14.4.1    | Interrupt Sources                                              | 368 |

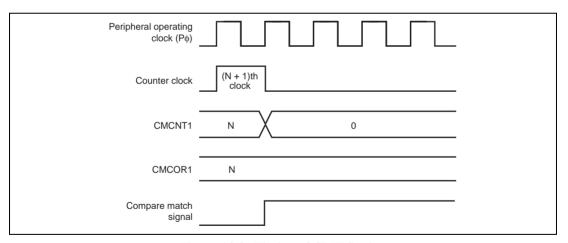

|       | 14.4.2    | Timing of Setting Compare Match Flag                           | 368 |

|       | 14.4.3    | Timing of Clearing Compare Match Flag                          | 368 |

| 14.5  | Usage N   | lotes                                                          | 369 |

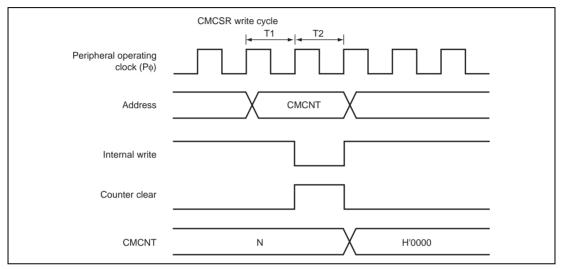

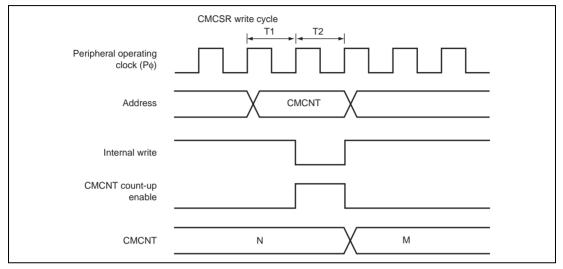

|       | 14.5.1    | Conflict between Write and Compare-Match Processes of CMCNT         | 369 |

|-------|-----------|---------------------------------------------------------------------|-----|

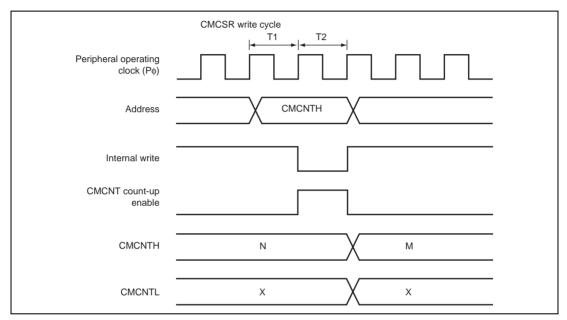

|       | 14.5.2    | Conflict between Word-Write and Count-Up Processes of CMCNT         | 370 |

|       | 14.5.3    | Conflict between Byte-Write and Count-Up Processes of CMCNT         | 371 |

|       | 14.5.4    | Conflict between Write Processes to CMCNT with the Counting Stopped |     |

|       |           | and CMCOR                                                           | 371 |

|       |           |                                                                     |     |

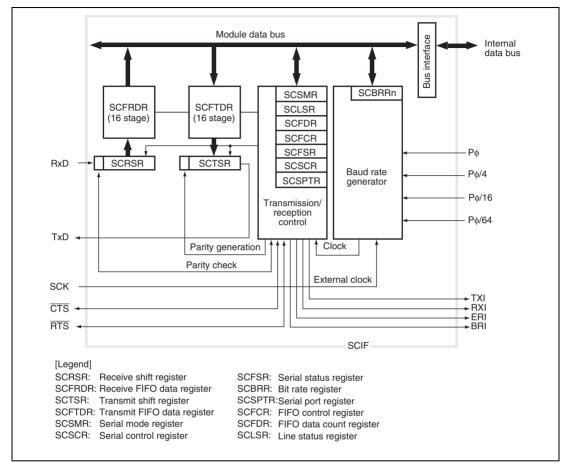

| Secti | ion 15 Se | erial Communication Interface with FIFO (SCIF)                      | 373 |

| 15.1  | Overvie   | W                                                                   | 373 |

|       | 15.1.1    | Features                                                            | 373 |

| 15.2  | Pin Con   | figuration                                                          | 376 |

| 15.3  | Register  | Description                                                         | 377 |

|       | 15.3.1    | Receive Shift Register (SCRSR)                                      | 378 |

|       | 15.3.2    | Receive FIFO Data Register (SCFRDR)                                 | 378 |

|       | 15.3.3    | Transmit Shift Register (SCTSR)                                     | 378 |

|       | 15.3.4    | Transmit FIFO Data Register (SCFTDR)                                | 379 |

|       | 15.3.5    | Serial Mode Register (SCSMR)                                        | 379 |

|       | 15.3.6    | Serial Control Register (SCSCR)                                     | 382 |

|       | 15.3.7    | Serial Status Register (SCFSR)                                      | 386 |

|       | 15.3.8    | Bit Rate Register (SCBRR)                                           | 394 |

|       | 15.3.9    | FIFO Control Register (SCFCR)                                       | 401 |

|       | 15.3.10   | FIFO Data Count Register (SCFDR)                                    | 404 |

|       | 15.3.11   | Serial Port Register (SCSPTR)                                       | 405 |

|       | 15.3.12   | Line Status Register (SCLSR)                                        | 409 |

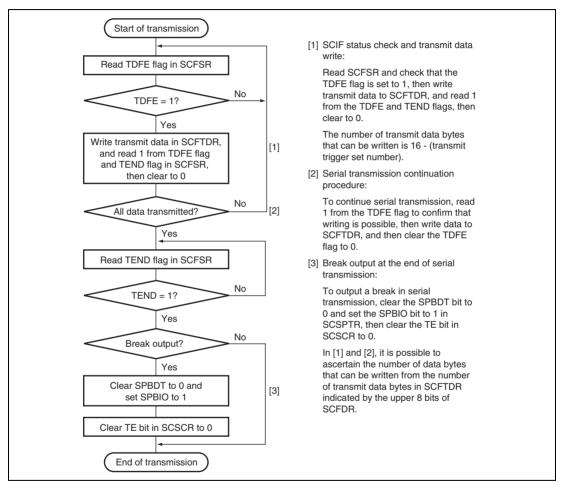

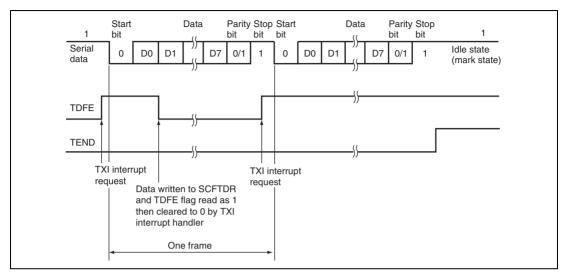

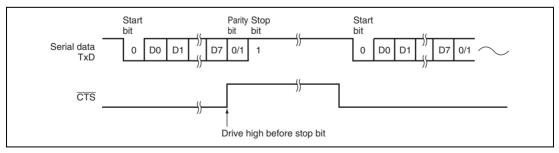

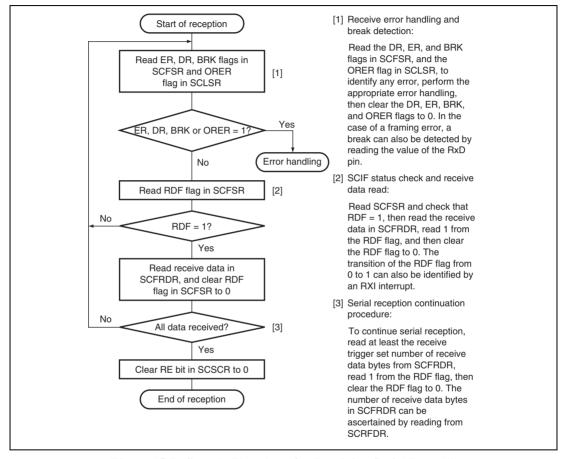

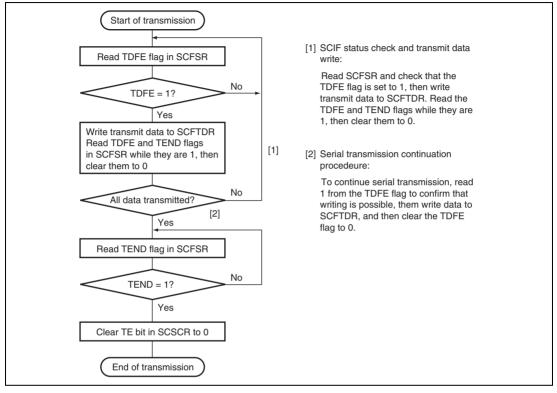

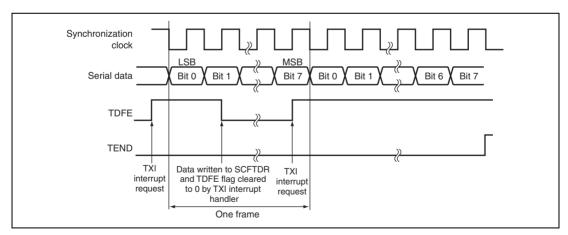

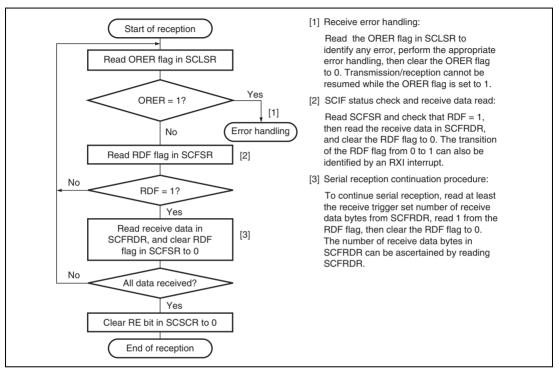

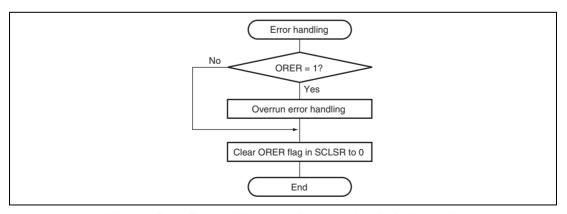

| 15.4  | Operation | on                                                                  | 410 |

|       | 15.4.1    | Overview                                                            | 410 |

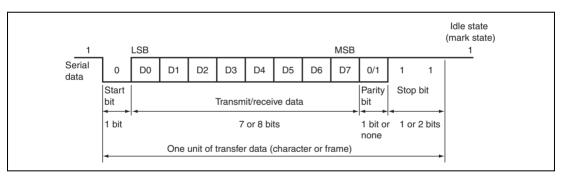

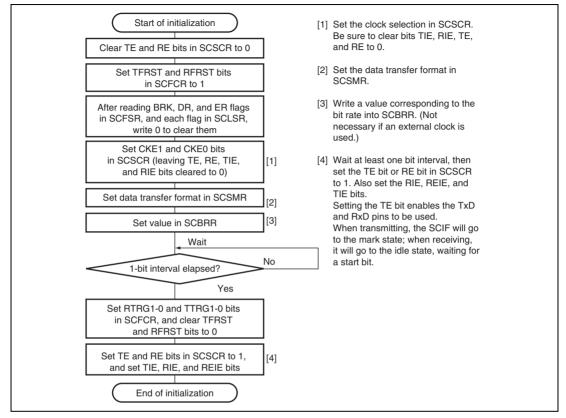

|       | 15.4.2    | Operation in Asynchronous Mode                                      | 412 |

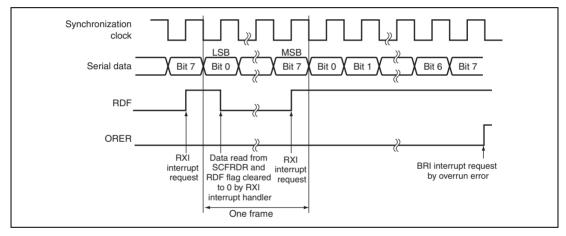

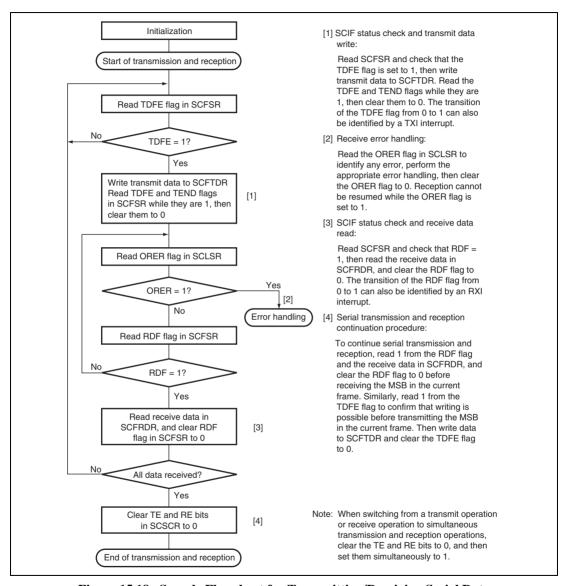

|       | 15.4.3    | Synchronous Mode                                                    | 423 |

| 15.5  | SCIF Int  | terrupts                                                            | 431 |

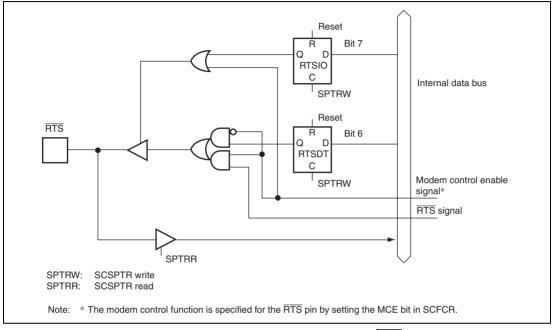

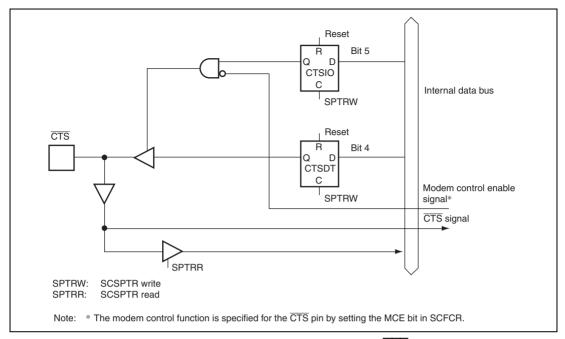

| 15.6  | Serial Po | ort Register (SCSPTR) and SCIF Pins                                 | 432 |

| 15.7  | Usage N   | Totes                                                               | 436 |

| ~     |           | 1.17/011.7770./3707                                                 |     |

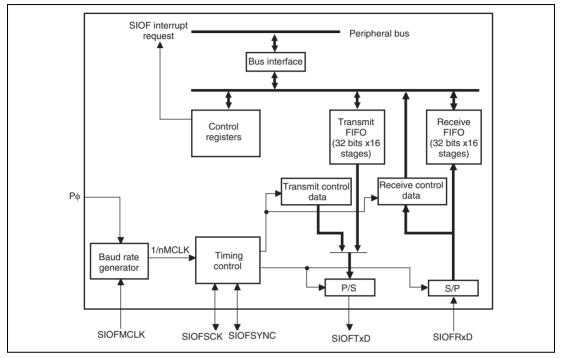

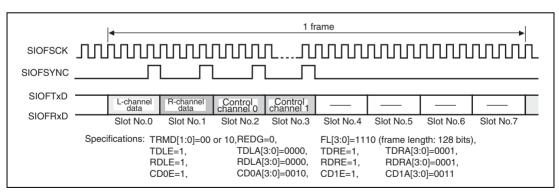

|       |           | erial I/O with FIFO (SIOF)                                          |     |

| 16.1  |           |                                                                     |     |

| 16.2  | -         | utput Pins                                                          |     |

| 16.3  | _         | Descriptions                                                        |     |

|       | 16.3.1    | Mode Register (SIMDR)                                               |     |

|       | 16.3.2    | Control Register (SICTR)                                            |     |

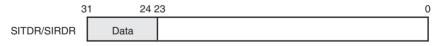

|       | 16.3.3    | Transmit Data Register (SITDR)                                      |     |

|       | 16.3.4    | Receive Data Register (SIRDR)                                       |     |

|       | 16.3.5    | Transmit Control Data Register (SITCR)                              | 453 |

|       | 16.3.6             | Receive Control Data Register (SIRCR)             | 454 |

|-------|--------------------|---------------------------------------------------|-----|

|       | 16.3.7             | Status Register (SISTR)                           | 455 |

|       | 16.3.8             | Interrupt Enable Register (SIIER)                 | 461 |

|       | 16.3.9             | FIFO Control Register (SIFCTR)                    | 463 |

|       | 16.3.10            | Clock Select Register (SISCR)                     | 465 |

|       | 16.3.11            | Transmit Data Assign Register (SITDAR)            | 466 |

|       | 16.3.12            | Receive Data Assign Register (SIRDAR)             | 468 |

|       | 16.3.13            | Control Data Assign Register (SICDAR)             | 469 |

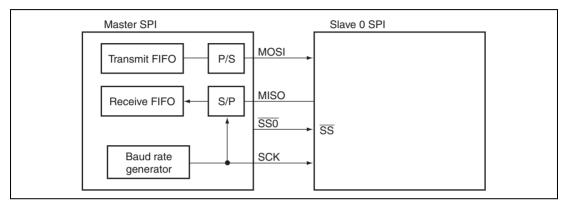

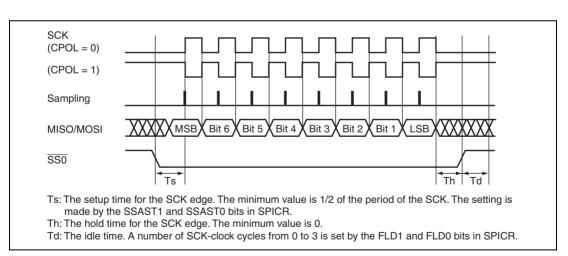

|       | 16.3.14            | SPI Control Register (SPICR)                      | 470 |

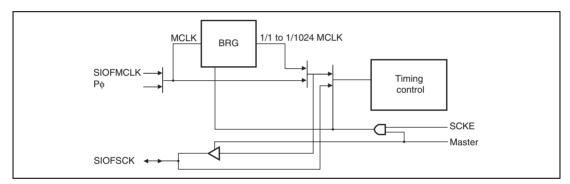

| 16.4  | Operatio           | on                                                | 473 |

|       | 16.4.1             | Serial Clocks                                     | 473 |

|       | 16.4.2             | Serial Timing                                     | 474 |

|       | 16.4.3             | Transfer Data Format                              | 475 |

|       | 16.4.4             | Register Allocation of Transfer Data              | 477 |

|       | 16.4.5             | Control Data Interface                            | 479 |

|       | 16.4.6             | FIFO                                              | 481 |

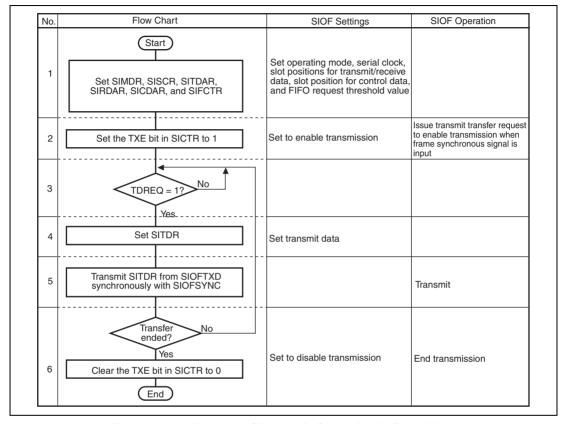

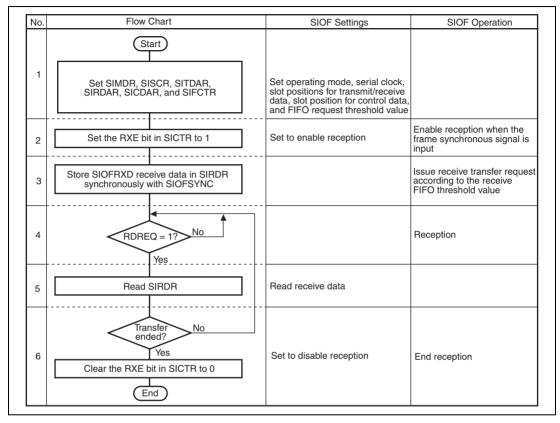

|       | 16.4.7             | Transmit and Receive Procedures                   | 483 |

|       | 16.4.8             | Interrupts                                        | 488 |

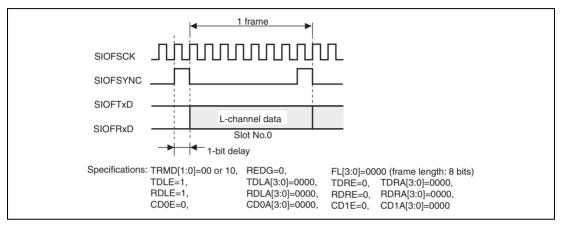

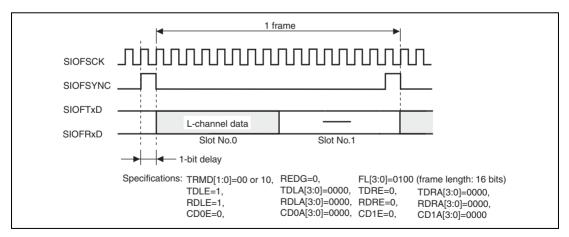

|       | 16.4.9             | Transmit and Receive Timing                       | 490 |

|       | 16.4.10            | SPI Mode                                          | 494 |

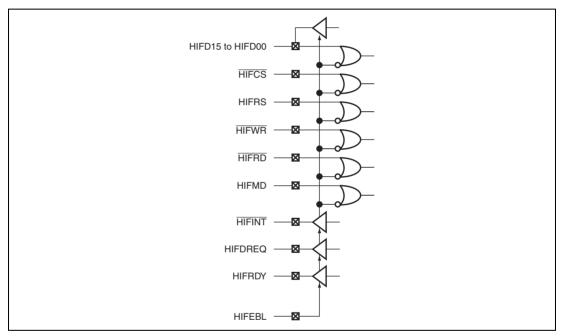

| Secti | ion 17 H           | ost Interface (HIF)                               | 503 |

| 17.1  |                    | ost interface (Tiff )                             |     |

| 17.1  |                    | ıtput Pins                                        |     |

| 17.2  | -                  | Access                                            |     |

| 17.5  | 17.3.1             | Operation                                         |     |

|       | 17.3.1             | Connection Method.                                |     |

| 17.4  |                    | Descriptions                                      |     |

| 17.7  | 17.4.1             | HIF Index Register (HIFIDX).                      |     |

|       | 17.4.1             | HIF General Status Register (HIFGSR)              |     |

|       | 17.4.3             | HIF Status/Control Register (HIFSCR)              |     |

|       | 17.4.4             | HIF Memory Control Register (HIFMCR)              |     |

|       | 17.4.5             | HIF Internal Interrupt Control Register (HIFIICR) |     |

|       | 17.4.6             | HIF External Interrupt Control Register (HIFEICR) |     |

|       | 17.4.7             | HIF Address Register (HIFADR)                     |     |

|       | 17.4.8             | HIF Data Register (HIFDATA)                       |     |

|       | 17.4.9             | HIF Boot Control Register (HIFBCR)                |     |

|       |                    |                                                   |     |

|       |                    | HIFDREO Trigger Register (HIFDTR)                 | 518 |

|       | 17.4.10<br>17.4.11 | HIFDREQ Trigger Register (HIFDTR)                 |     |

| 17.6    | Interface | e (Basic)                                                           | 522   |

|---------|-----------|---------------------------------------------------------------------|-------|

| 17.7    | Interface | e (Details)                                                         | 523   |

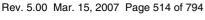

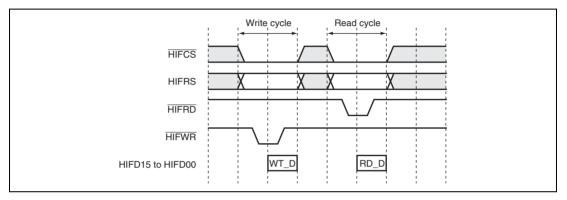

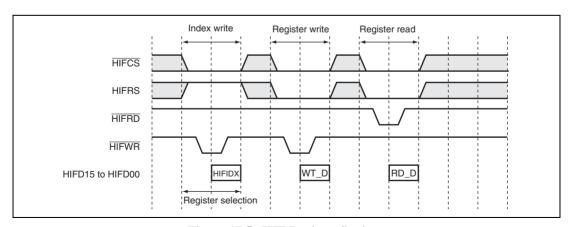

|         | 17.7.1    | HIFIDX Write/HIFGSR Read                                            | 523   |

|         | 17.7.2    | Reading/Writing of HIF Registers other than HIFIDX and HIFGSR       | 523   |

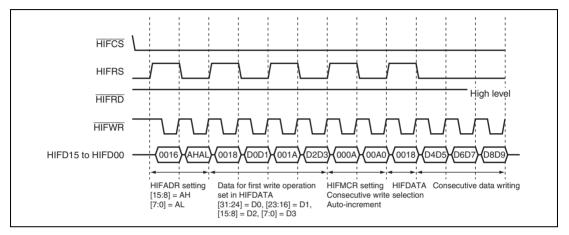

|         | 17.7.3    | Consecutive Data Writing to HIFRAM by External Device               | 524   |

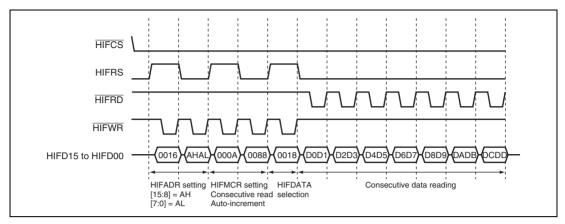

|         | 17.7.4    | Consecutive Data Reading from HIFRAM to External Device             | 524   |

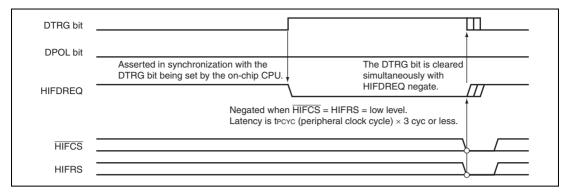

| 17.8    | External  | DMAC Interface                                                      | 525   |

| 17.9    | Alignme   | ent Control                                                         | 531   |

| 17.10   | Interface | e When External Device Power is Cut Off                             | 532   |

| Section | on 18 Pi  | n Function Controller (PFC)                                         | .535  |

| 18.1    | Register  | Descriptions                                                        | 545   |

|         | 18.1.1    | Port A IO Register H (PAIORH)                                       | 546   |

|         | 18.1.2    | Port A Control Register H1 and H2 (PACRH1 and PACRH2)               | 546   |

|         | 18.1.3    | Port B IO Register L (PBIORL)                                       | 549   |

|         | 18.1.4    | Port B Control Register L1 and L2 (PBCRL1 and PBCRL2)               | 549   |

|         | 18.1.5    | Port C IO Register H and L (PCIORH and PCIORL)                      | 553   |

|         | 18.1.6    | Port C Control Register H2, L1, and L2 (PCCRH2, PCCRL1, and PCCRL2) | . 553 |

|         | 18.1.7    | Port D IO Register L (PDIORL)                                       | 558   |

|         | 18.1.8    | Port D Control Register L2 (PDCRL2)                                 | 559   |

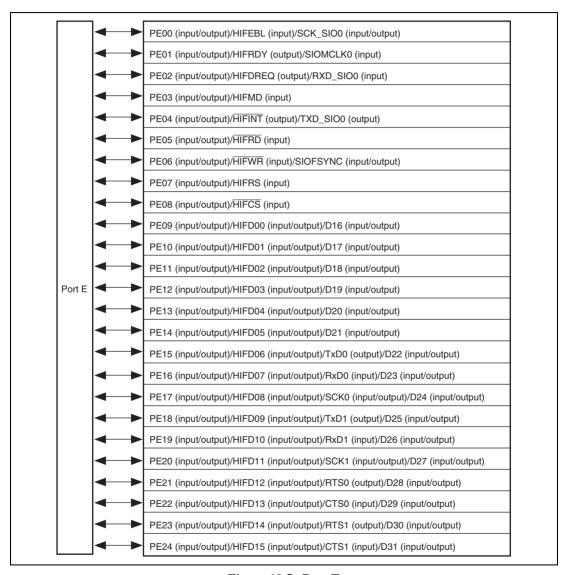

|         | 18.1.9    | Port E IO Register H and L (PEIORH and PEIORL)                      | 561   |

|         | 18.1.10   | Port E Control Register H1, H2, L1, and L2 (PECRH1, PECRH2, PECRL1, |       |

|         |           | and PECRL2)                                                         | 561   |

| Section | on 19 I/0 | O Ports                                                             | .569  |

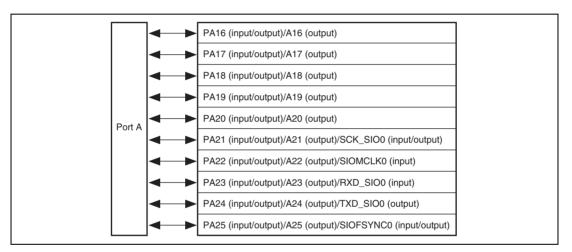

| 19.1    | Port A    |                                                                     | 569   |

|         | 19.1.1    | Register Description                                                | 569   |

|         | 19.1.2    | Port A Data Register H (PADRH)                                      |       |

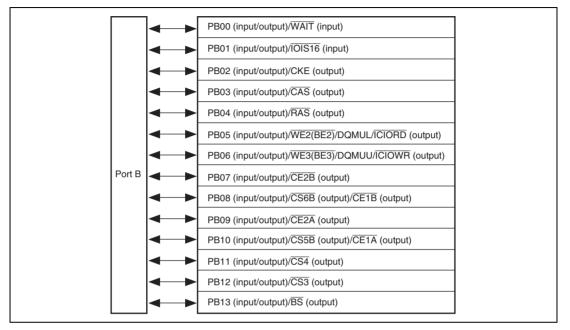

| 19.2    | Port B    | -                                                                   | 571   |

|         | 19.2.1    | Register Description                                                | 571   |

|         | 19.2.2    | Port B Data Register L (PBDRL)                                      | 571   |

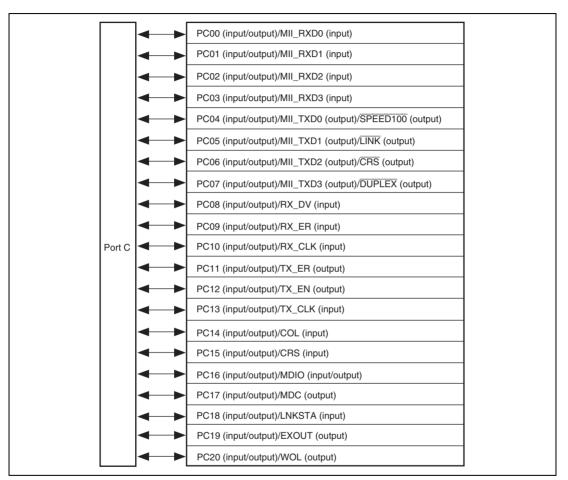

| 19.3    | Port C    | -                                                                   | 573   |

|         | 19.3.1    | Register Description                                                | 574   |

|         | 19.3.2    | Port C Data Registers H and L (PCDRH and PCDRL)                     |       |

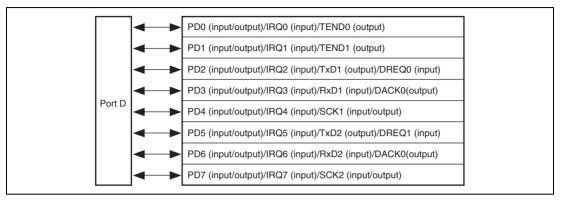

| 19.4    | Port D    |                                                                     |       |

|         | 19.4.1    | Register Description                                                | 576   |

|         | 19.4.2    | Port D Data Register L (PDDRL)                                      | 576   |

| 19.5  | Port E    |                                                 | 578 |

|-------|-----------|-------------------------------------------------|-----|

|       | 19.5.1    | Register Description                            | 579 |

|       | 19.5.2    | Port E Data Registers H and L (PEDRH and PEDRL) | 579 |

| 19.6  | Usage N   | lotes                                           | 581 |

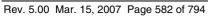

| Secti | ion 20 U  | ser Break Controller (UBC)                      | 583 |

| 20.1  |           | 5                                               |     |

| 20.2  | Register  | Descriptions                                    | 585 |

|       | 20.2.1    | Break Address Register A (BARA)                 | 585 |

|       | 20.2.2    | Break Address Mask Register A (BAMRA)           | 586 |

|       | 20.2.3    | Break Bus Cycle Register A (BBRA)               | 586 |

|       | 20.2.4    | Break Address Register B (BARB)                 | 587 |

|       | 20.2.5    | Break Address Mask Register B (BAMRB)           | 588 |

|       | 20.2.6    | Break Data Register B (BDRB)                    | 588 |

|       | 20.2.7    | Break Data Mask Register B (BDMRB)              |     |

|       | 20.2.8    | Break Bus Cycle Register B (BBRB)               | 589 |

|       | 20.2.9    | Break Control Register (BRCR)                   | 591 |

|       | 20.2.10   | Execution Times Break Register (BETR)           |     |

|       | 20.2.11   | Branch Source Register (BRSR)                   |     |

|       | 20.2.12   | Branch Destination Register (BRDR)              | 595 |

| 20.3  | Operation | on                                              |     |

|       | 20.3.1    | Flow of User Break Operation                    | 596 |

|       | 20.3.2    | Break on Instruction Fetch Cycle                |     |

|       | 20.3.3    | Break on Data Access Cycle                      |     |

|       | 20.3.4    | Sequential Break                                | 598 |

|       | 20.3.5    | Value of Saved Program Counter (PC)             |     |

|       | 20.3.6    | PC Trace                                        |     |

|       | 20.3.7    | Usage Examples                                  | 600 |

|       | 20.3.8    | Notes                                           |     |

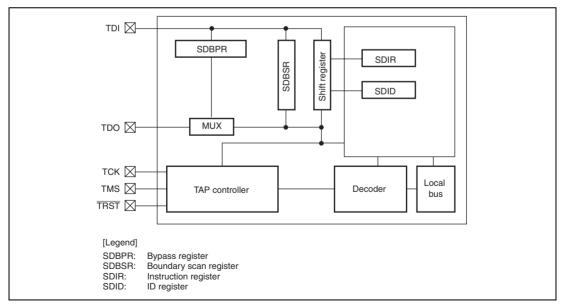

| Secti | ion 21 U  | ser Debugging Interface (H-UDI)                 | 605 |

| 21.1  |           | 5                                               |     |

| 21.2  |           | utput Pins                                      |     |

| 21.3  | -         | Descriptions                                    |     |

|       | 21.3.1    | Bypass Register (SDBPR)                         |     |

|       | 21.3.2    | Instruction Register (SDIR)                     |     |

|       | 21.3.3    | Boundary Scan Register (SDBSR)                  |     |

|       | 21.3.4    | ID Register (SDID)                              |     |

| 21.4  |           | on                                              |     |

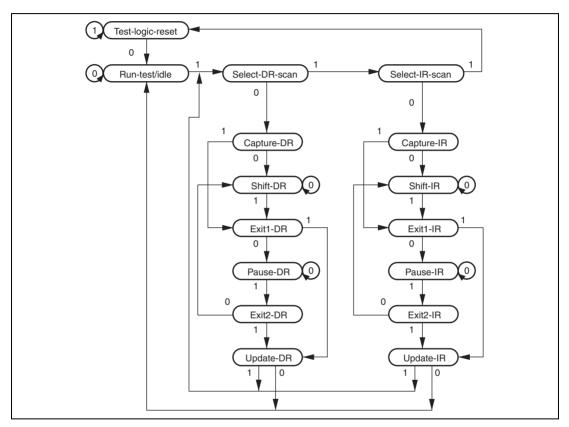

|       | 21.4.1    | TAP Controller                                  |     |

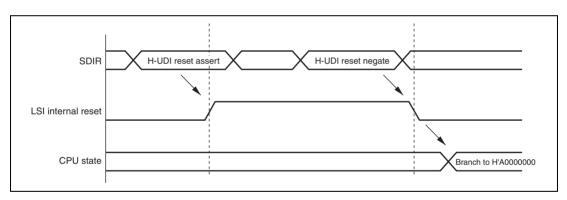

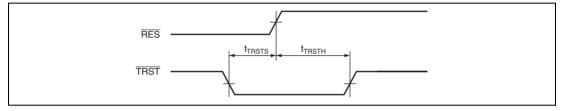

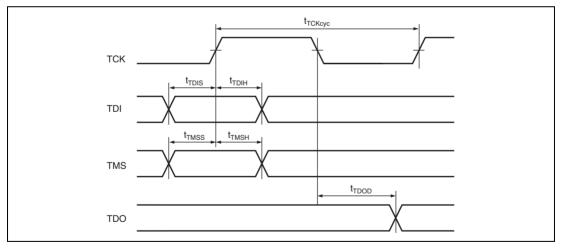

|         | 21.4.2    | Reset Configuration                           | 617 |

|---------|-----------|-----------------------------------------------|-----|

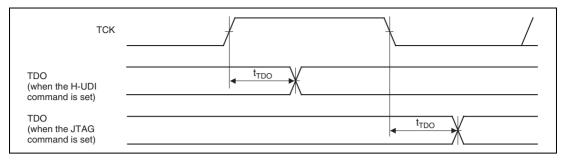

|         | 21.4.3    | TDO Output Timing                             | 617 |

|         | 21.4.4    | H-UDI Reset                                   | 618 |

|         | 21.4.5    | H-UDI Interrupt                               | 618 |

| 21.5    | Boundar   | y Scan                                        | 619 |

|         | 21.5.1    | Supported Instructions                        | 619 |

|         | 21.5.2    | Points for Attention                          | 620 |

| 21.6    | Usage N   | otes                                          | 620 |

| Section | on 22 Et  | hernet Physical Layer Transceiver (PHY)       | 621 |

| 22.1    |           | ````                                          |     |

| 22.2    | Pin Conf  | Figuration                                    | 623 |

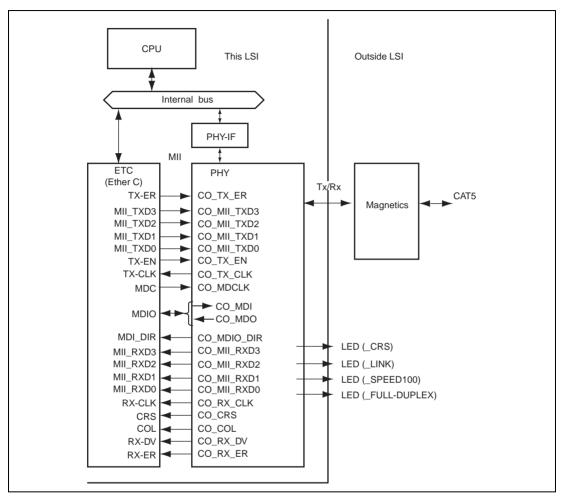

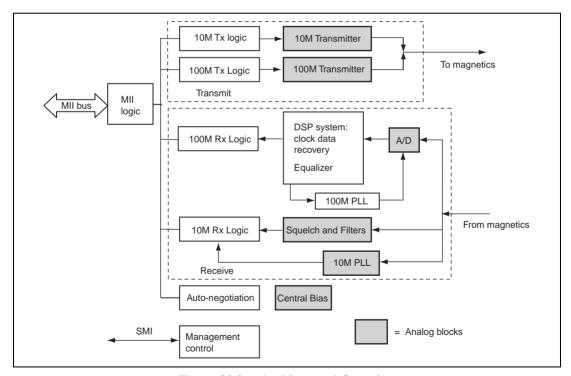

| 22.3    | Top Lev   | el Functional Architecture                    | 624 |

| 22.4    | -         | nagement Control                              |     |

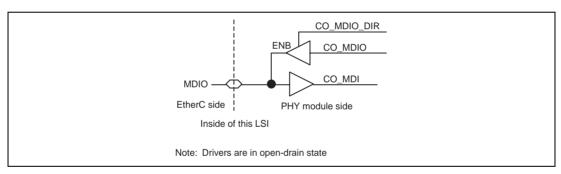

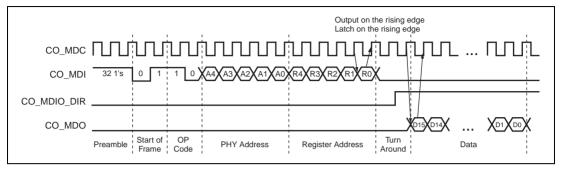

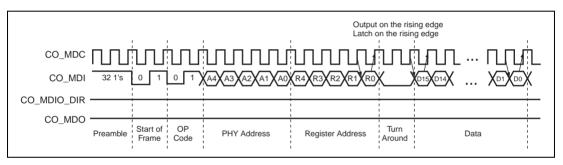

|         | 22.4.1    | Serial Management Interface (SMI)             | 625 |

|         | 22.4.2    | SMI Register Mapping                          | 632 |

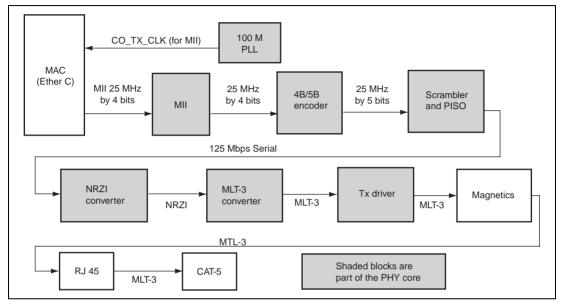

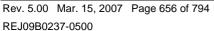

| 22.5    | 100Base   | -TX Transmit                                  | 638 |

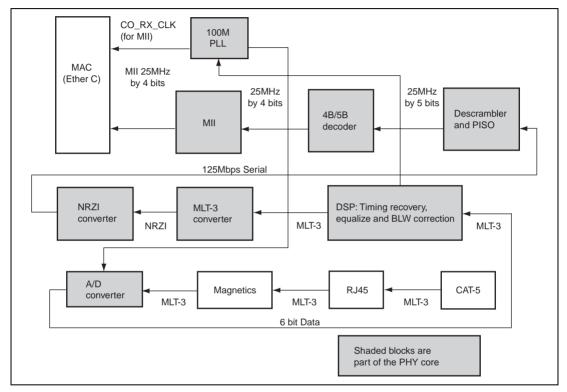

| 22.6    | 100Base   | -TX Receive                                   | 641 |

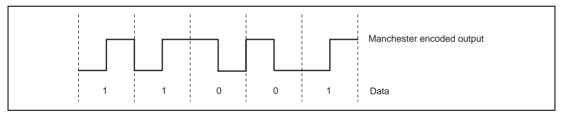

| 22.7    | 10Base-   | Γ Transmit                                    | 644 |

| 22.8    | 10Base-   | Г Receive                                     | 646 |

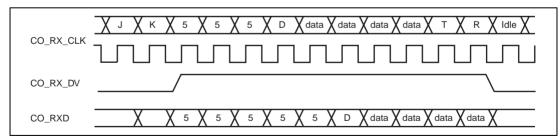

| 22.9    | MAC In    | terface                                       | 647 |

| 22.10   | Miscella  | neous Functions                               | 651 |

| 22.11   | Internal  | I/O Signals                                   | 655 |

| 22.12   | Signals I | Relevant to PHY-IF                            | 657 |

| 22.13   | Usage N   | otes                                          | 658 |

| 22.14   | Guidelin  | es for Layout                                 | 662 |

|         | 22.14.1   | General Guidelines                            | 662 |

|         | 22.14.2   | Guidelines for Layout                         | 663 |

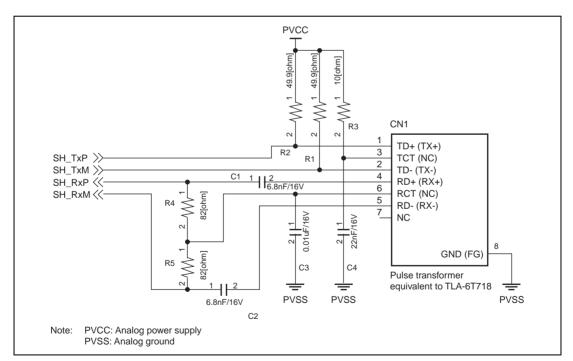

| Section | on 23 PH  | HY Interface (PHY-IF)                         | 667 |

| 23.1    |           |                                               |     |

| 23.2    | Register  | Descriptions                                  | 669 |

|         | 23.2.1    | PHY-IF Control Register (PHYIFCR)             | 669 |

|         | 23.2.2    | PHY-IF SMI Register 2 (PHYIFSMIR2)            | 670 |

|         | 23.2.3    | PHY-IF SMI Register 3 (PHYIFSMIR3)            | 671 |

|         | 23.2.4    | PHY-IF Address Register (PHYIFADDRR)          | 671 |

|         | 23.2.5    | PHY-IF status Register (PHYIFSR)              |     |

| 23.3    | PHY-IF    | Operation                                     | 673 |

|         | 23.3.1    | The Procedures of Setting Up the On-Chip PHY  | 673 |

|         | 23.3.2    | The Procedures of Set Up the External PHY LSI | 674 |

| Secti | ion 24 Li | st of Registers                                             | 675 |

|-------|-----------|-------------------------------------------------------------|-----|

| 24.1  | Register  | Addresses (Address Order)                                   | 676 |

| 24.2  | Register  | Bits                                                        | 684 |

| 24.3  | Register  | States in Each Processing State                             | 706 |

| Secti | ion 25 El | ectrical Characteristics                                    | 713 |

| 25.1  | Absolute  | e Maximum Ratings                                           | 713 |

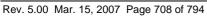

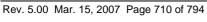

| 25.2  | Power-C   | On and Power-Off Order                                      | 714 |

| 25.3  | DC Chai   | racteristics                                                | 716 |

| 25.4  | AC Chai   | racteristics                                                | 718 |

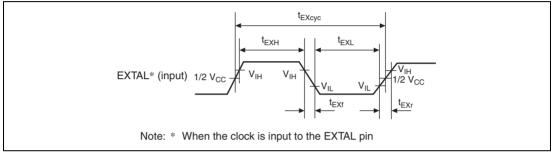

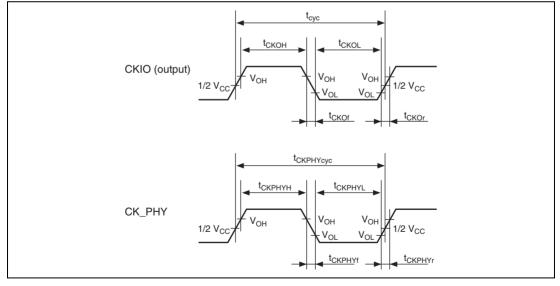

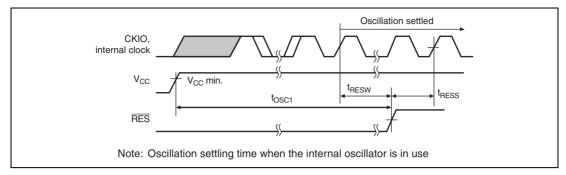

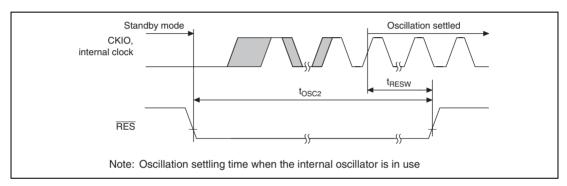

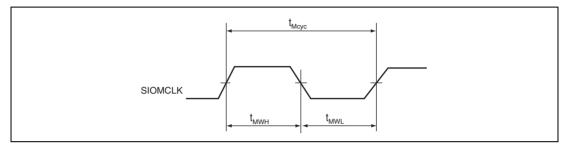

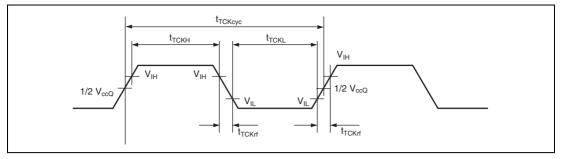

|       | 25.4.1    | Clock Timing                                                | 719 |

|       | 25.4.2    | Control Signal Timing                                       | 723 |

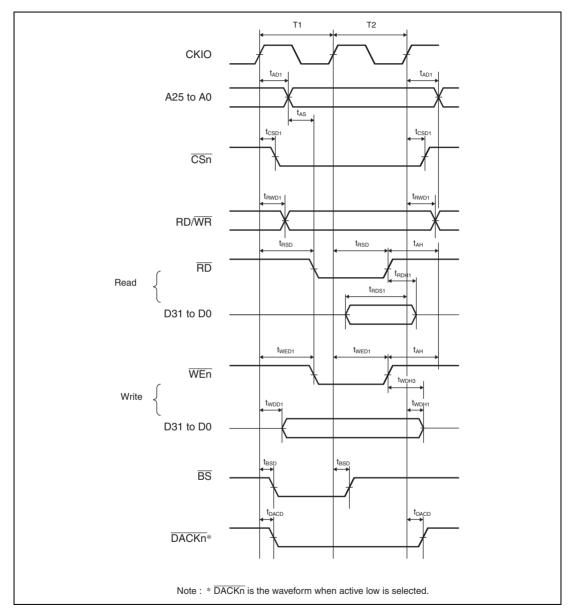

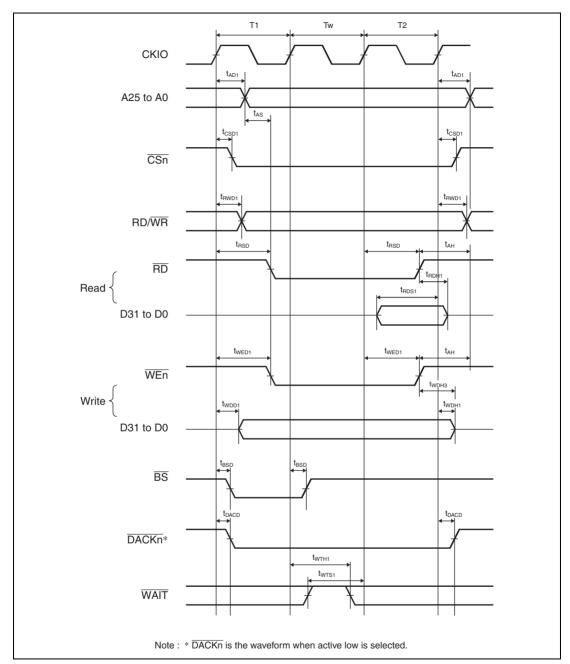

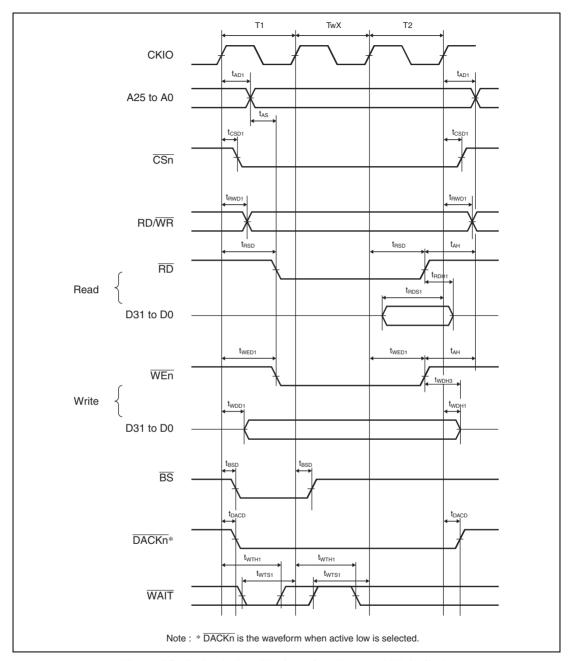

|       | 25.4.3    | AC Bus Timing                                               | 725 |

|       | 25.4.4    | Basic Timing                                                | 727 |

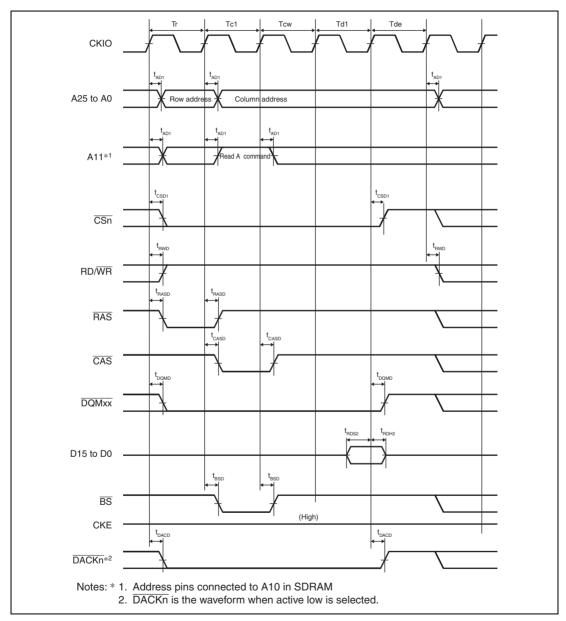

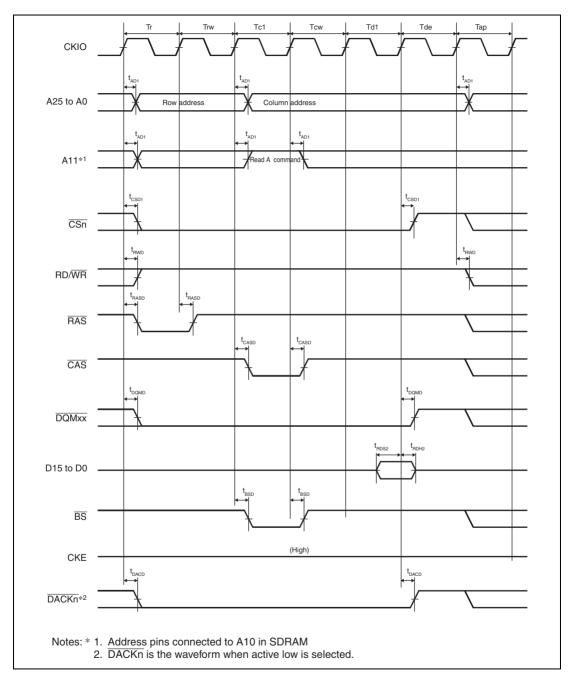

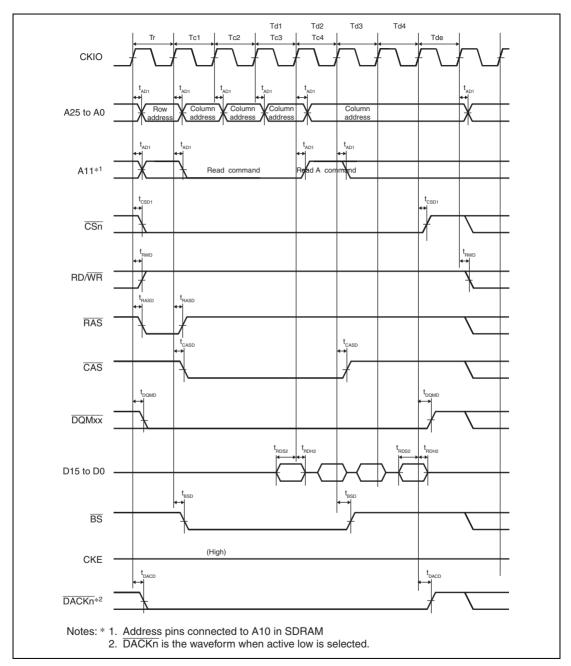

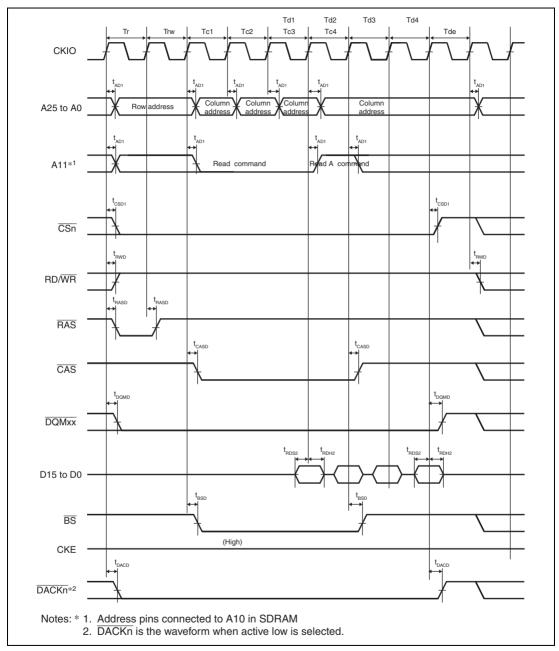

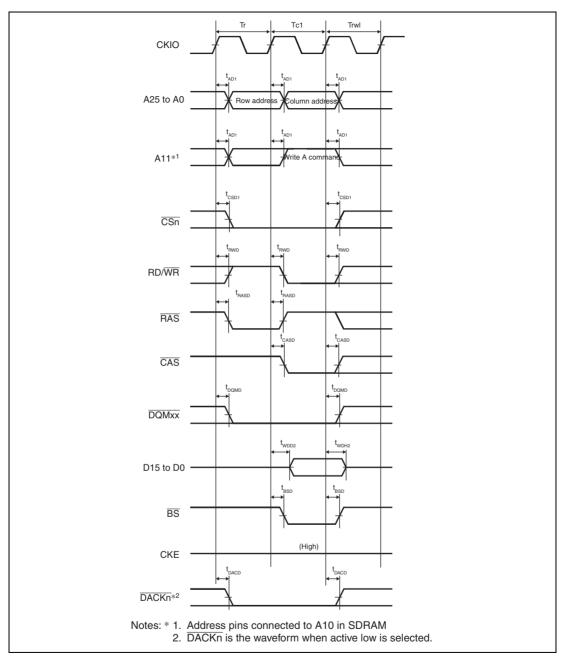

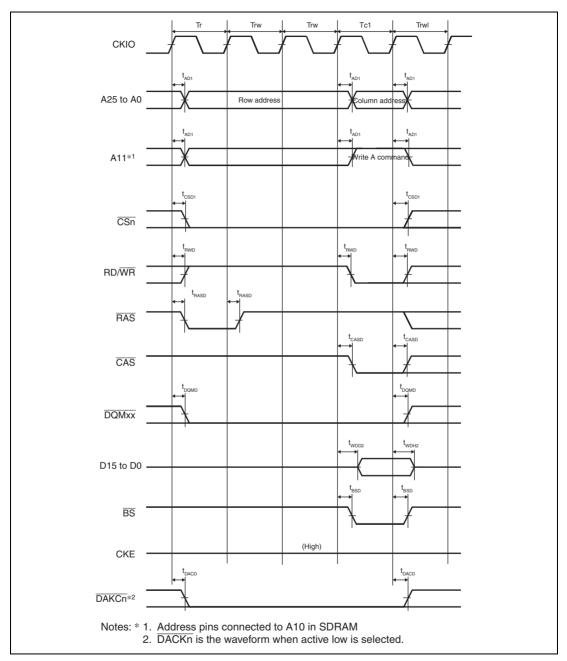

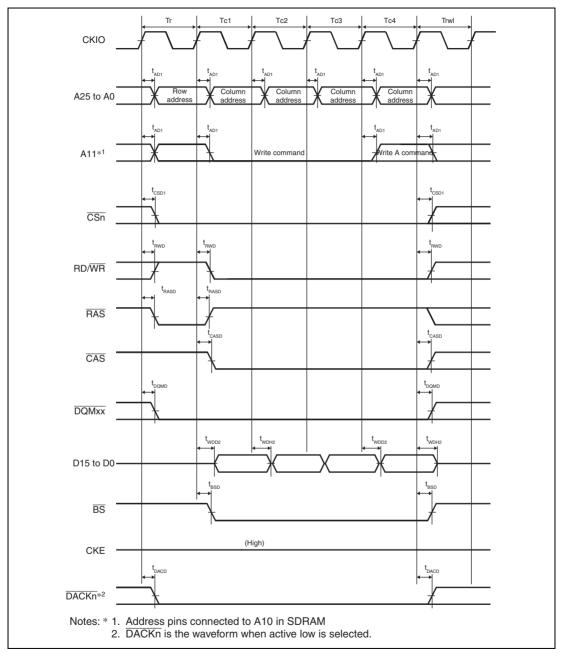

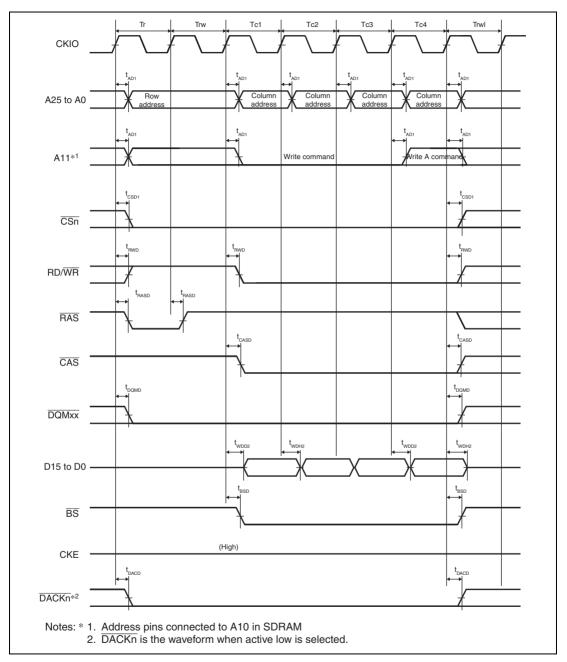

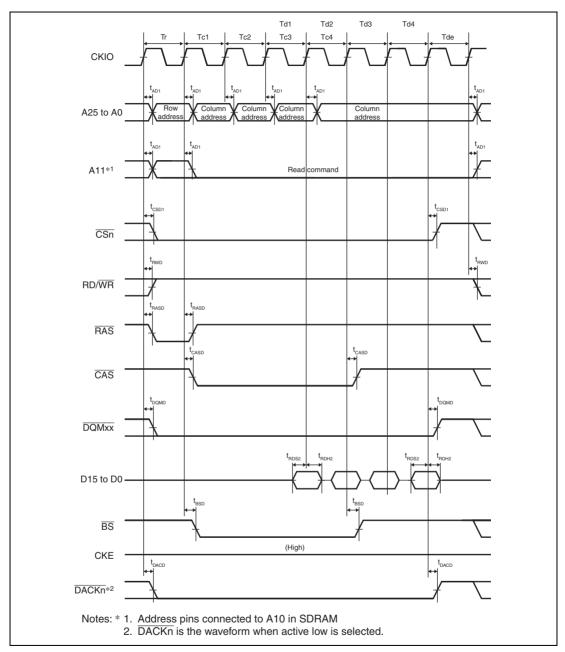

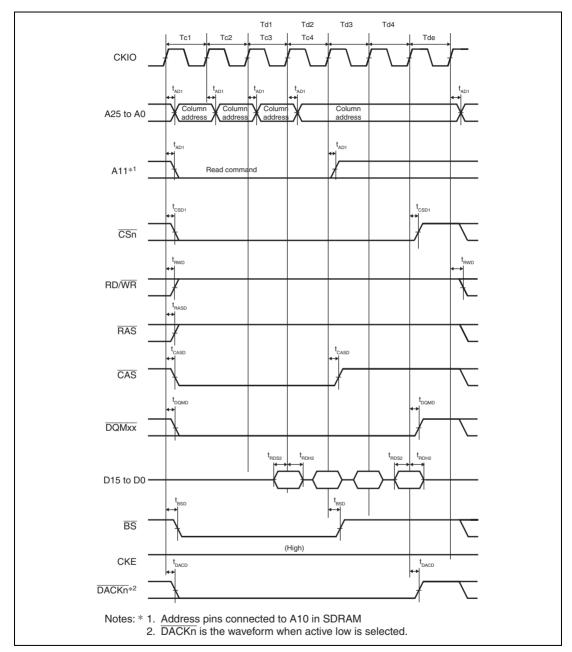

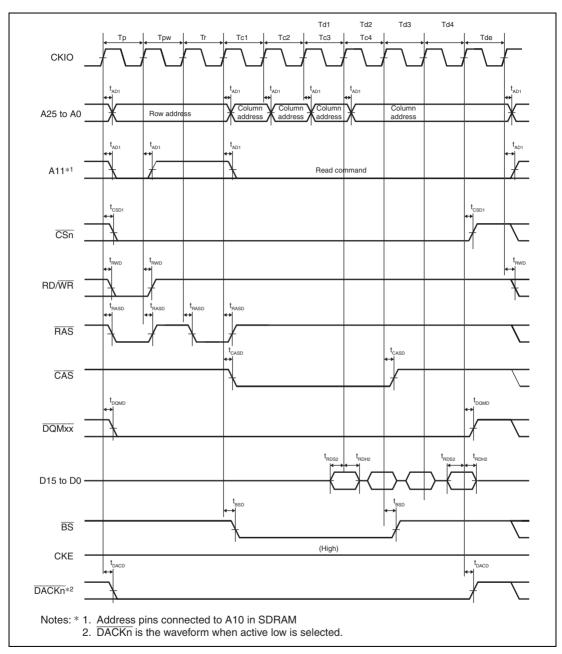

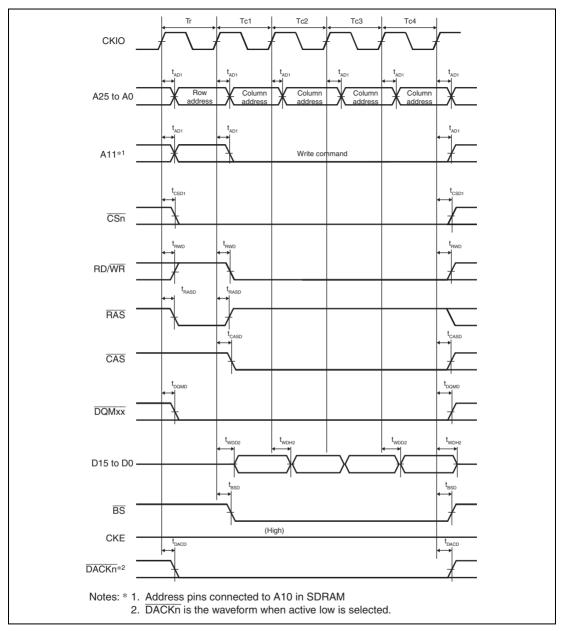

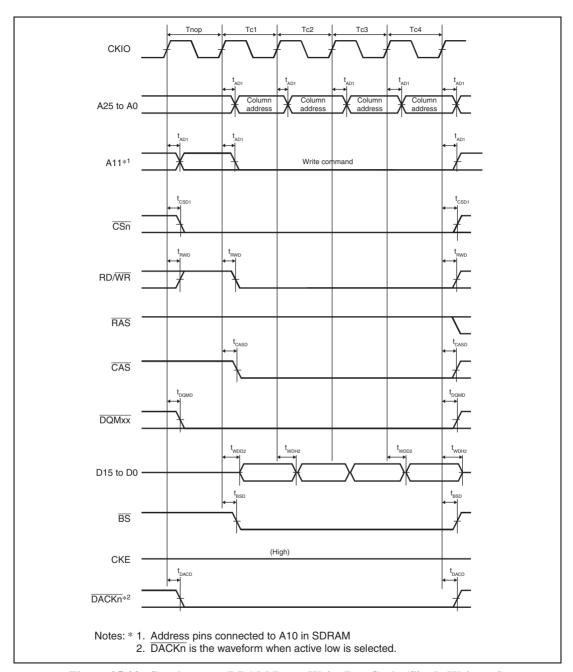

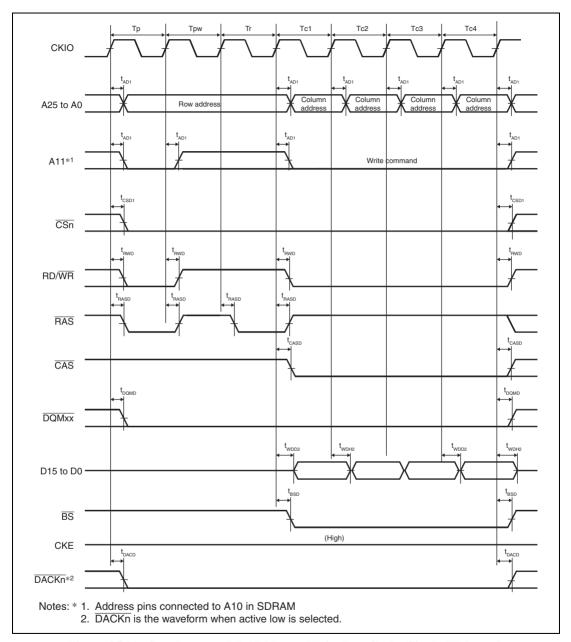

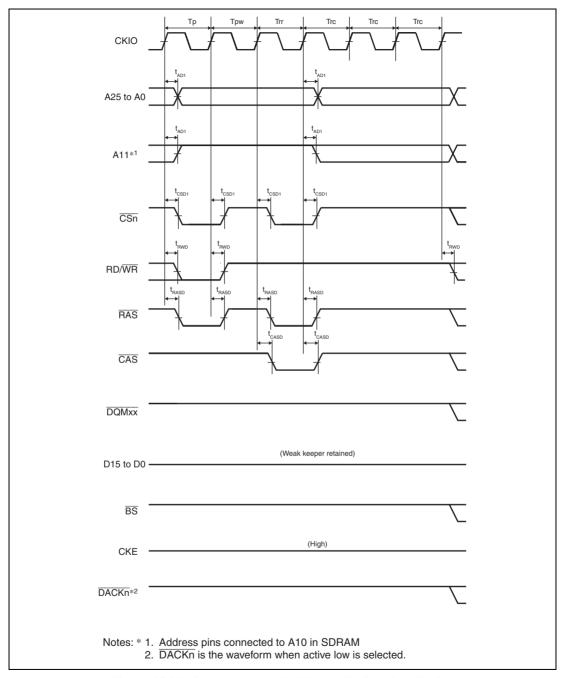

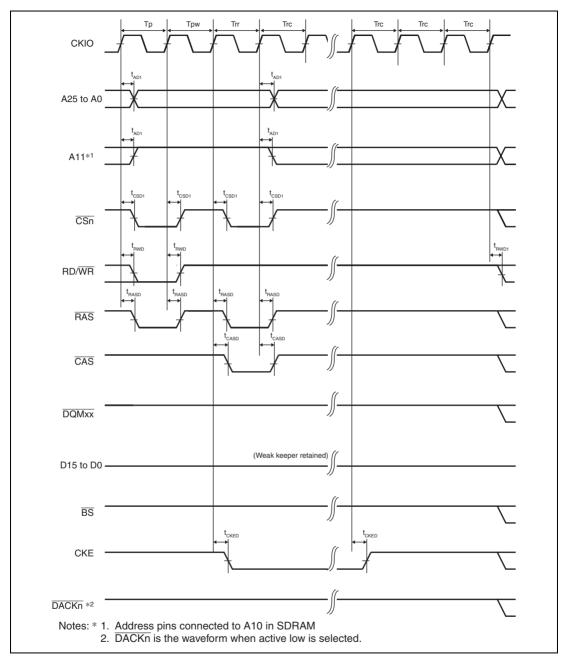

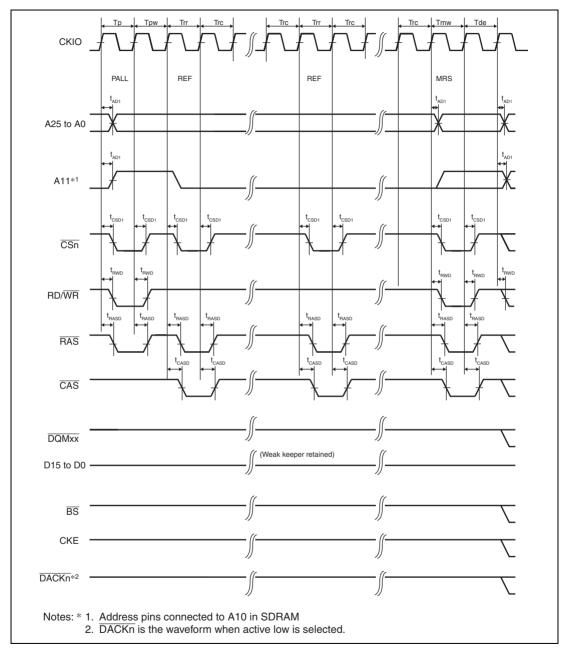

|       | 25.4.5    | Synchronous DRAM Timing                                     | 733 |

|       | 25.4.6    | PCMCIA Timing                                               | 750 |

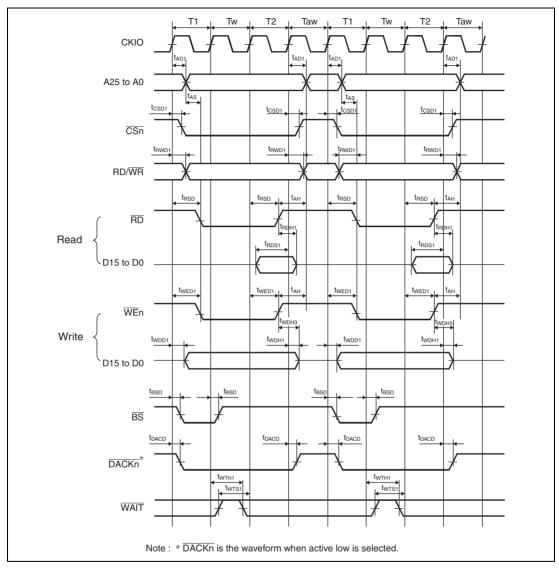

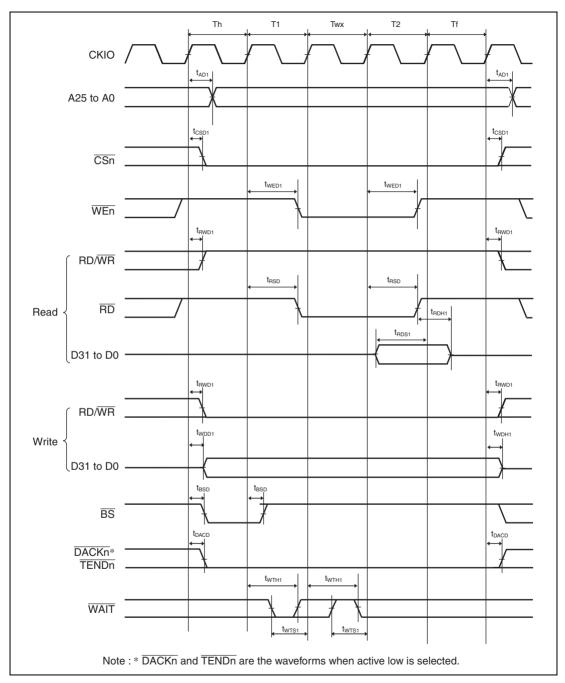

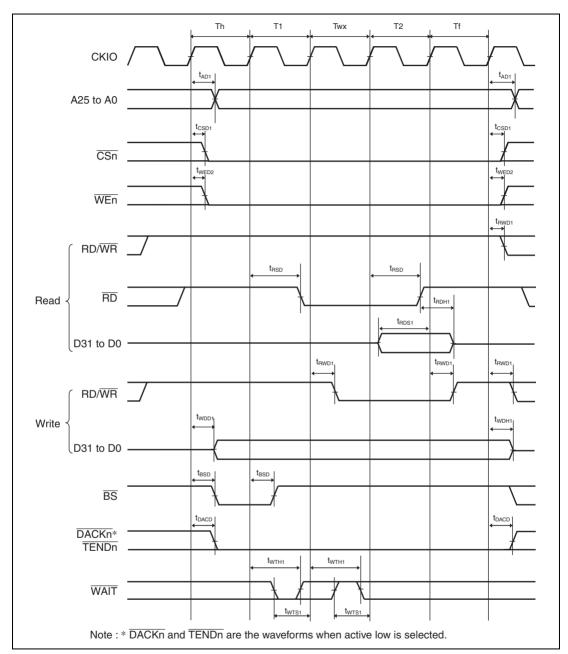

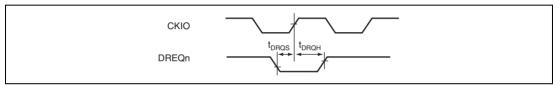

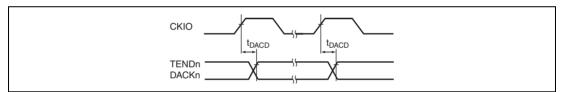

|       | 25.4.7    | DMAC Signal Timing                                          | 754 |

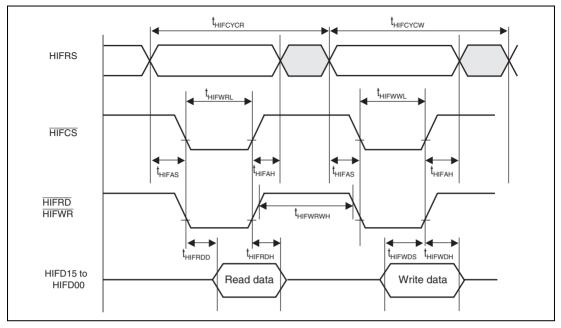

|       | 25.4.8    | SCIF Timing                                                 | 755 |

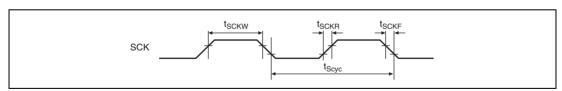

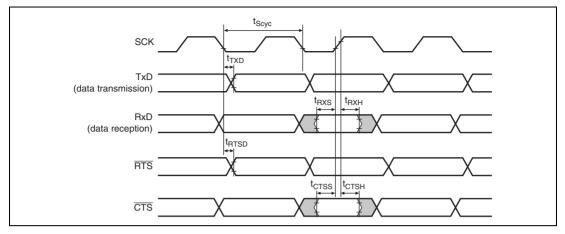

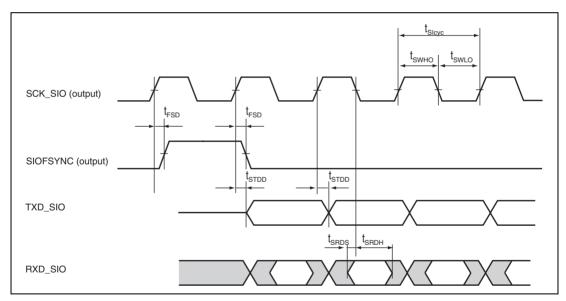

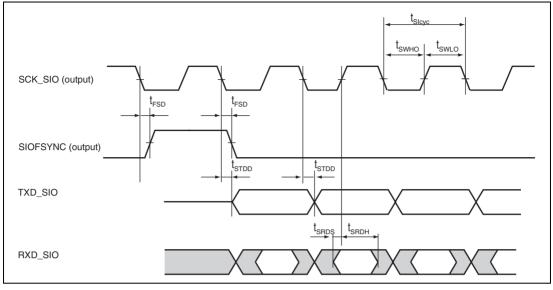

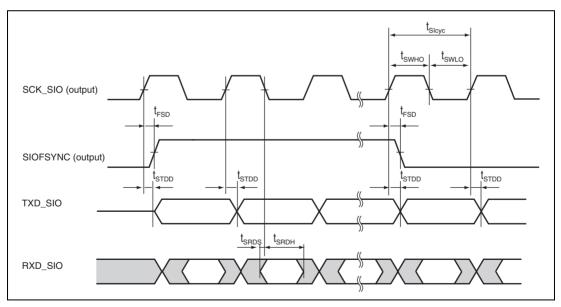

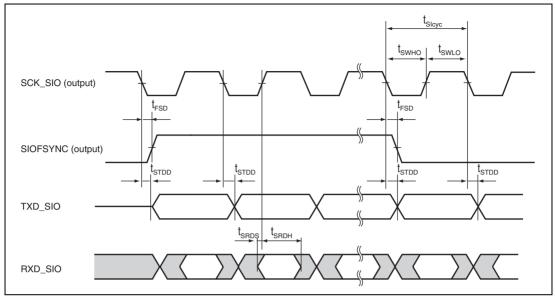

|       | 25.4.9    | SIOF Module Signal Timing                                   | 756 |

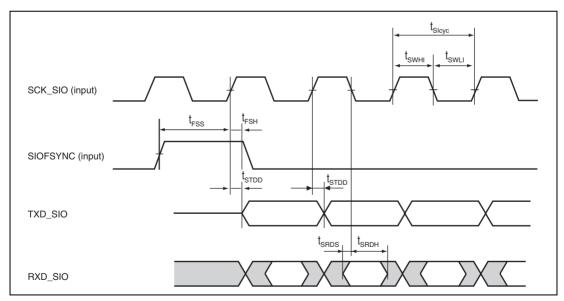

|       | 25.4.10   | Port Timing                                                 | 760 |

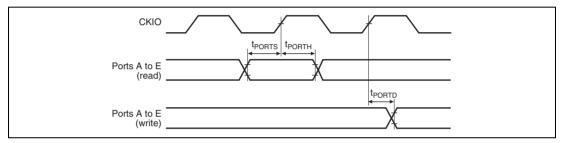

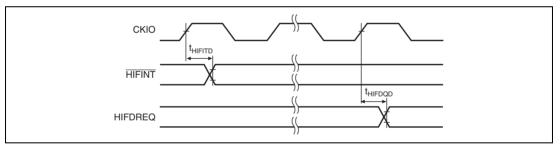

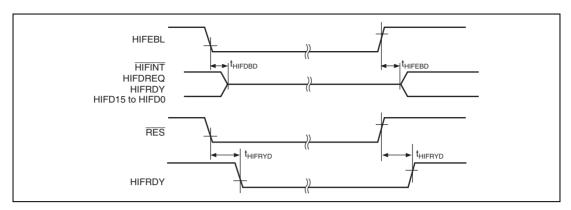

|       | 25.4.11   | HIF Timing                                                  | 761 |

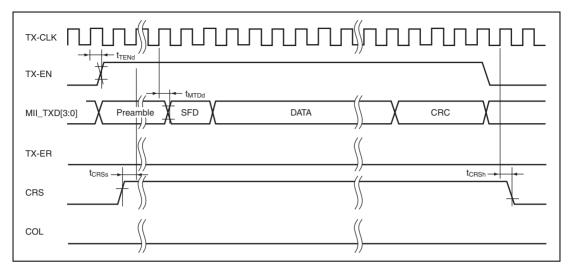

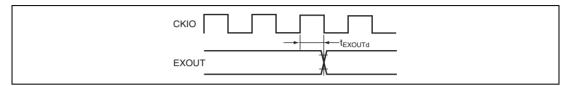

|       | 25.4.12   | EtherC Timing                                               | 764 |

|       | 25.4.13   | H-UDI Related Pin Timing                                    | 767 |

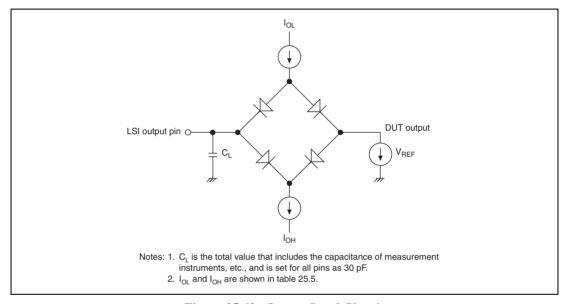

|       | 25.4.14   | AC Characteristic Test Conditions                           | 769 |

| 25.5  | Physical  | Layer Ttransceiver (PHY) Characteristics (Reference Values) | 770 |

| Appe  | endix     |                                                             | 771 |

| A.    |           | es in Each Pin State                                        |     |

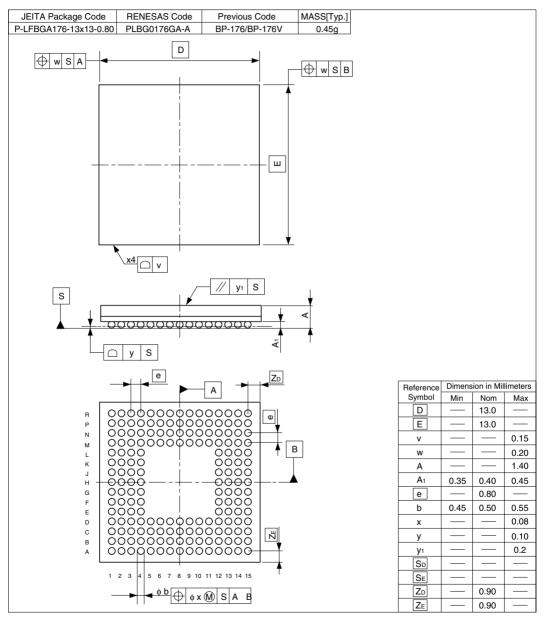

| B.    | Product   | Code Lineup                                                 | 776 |

| C.    |           | Dimensions                                                  |     |

| Mair  | n Revisio | ons and Additions in this Edition                           | 779 |

|       |           |                                                             |     |

# Figures

| Section 1   | Overview                                                                     |     |

|-------------|------------------------------------------------------------------------------|-----|

| Figure 1.1  | Block Diagram                                                                | 7   |

| Figure 1.2  | Pin Assignments                                                              | 8   |

| Section 2   | CPU                                                                          |     |

| Figure 2.1  | CPU Internal Register Configuration                                          | 24  |

| Figure 2.2  | Register Data Format                                                         | 28  |

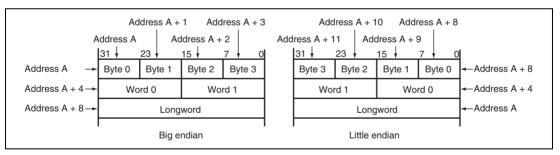

| Figure 2.3  | Memory Data Format                                                           | 28  |

| Figure 2.4  | CPU State Transition                                                         | 51  |

| Section 3   | Cache                                                                        |     |

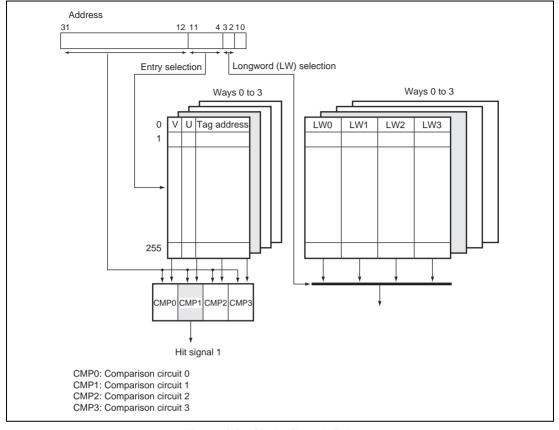

| _           | Cache Structure                                                              |     |

| -           | Cache Search Scheme                                                          |     |

| Figure 3.3  | Write-Back Buffer Configuration                                              | 59  |

| Figure 3.4  | Specifying Address and Data for Memory-Mapped Cache Access                   | 62  |

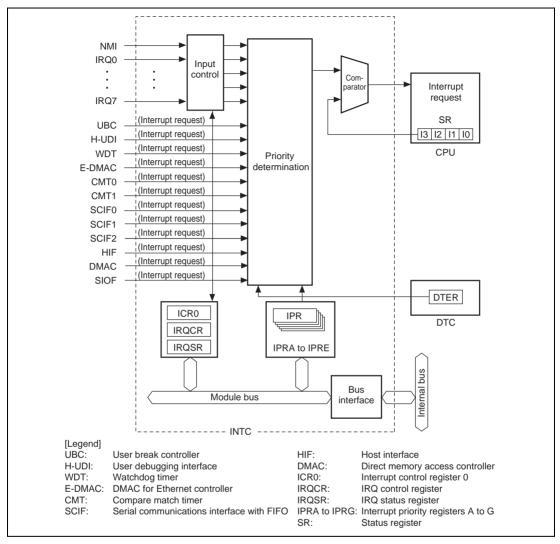

| Section 6   | Interrupt Controller (INTC)                                                  |     |

| _           | INTC Block Diagram                                                           |     |

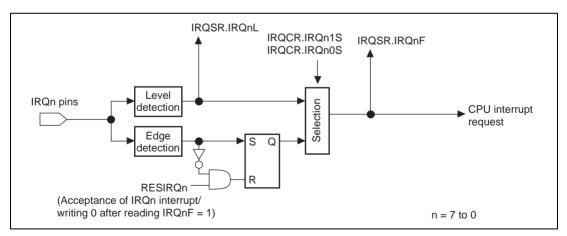

| Figure 6.2  | Block Diagram of IRQ7 to IRQ0 Interrupts Control                             | 98  |

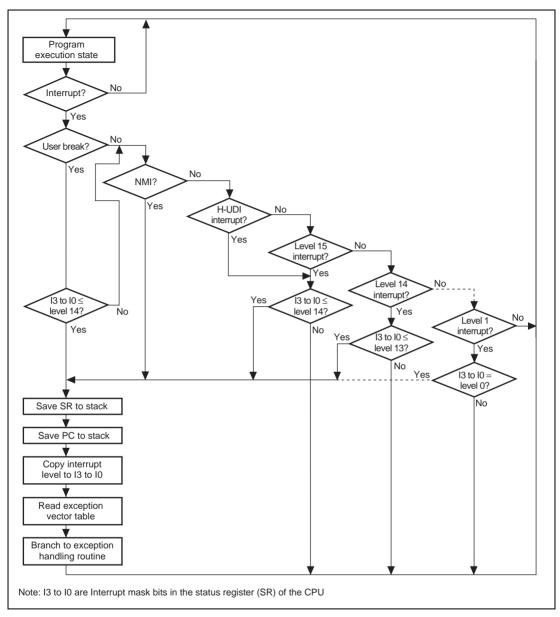

| -           | Interrupt Sequence Flowchart                                                 |     |

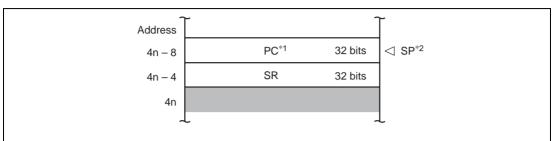

| Figure 6.4  | Stack after Interrupt Exception Handling                                     | 104 |

| Section 7   | Bus State Controller (BSC)                                                   |     |

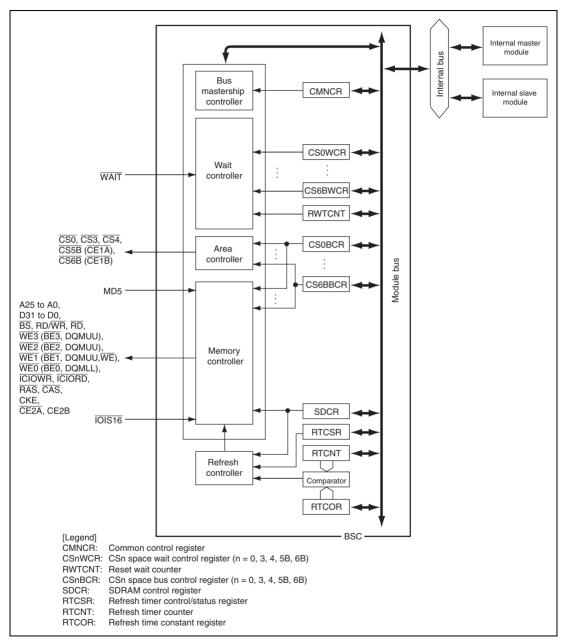

| Figure 7.1  | Block Diagram of BSC                                                         | 109 |

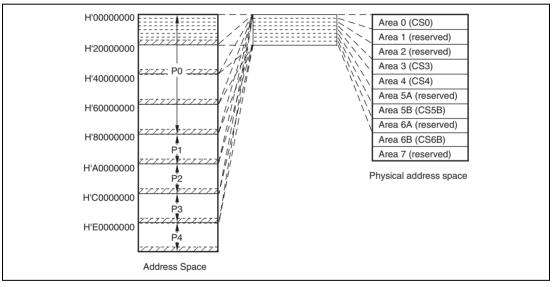

| -           | Address Space                                                                |     |

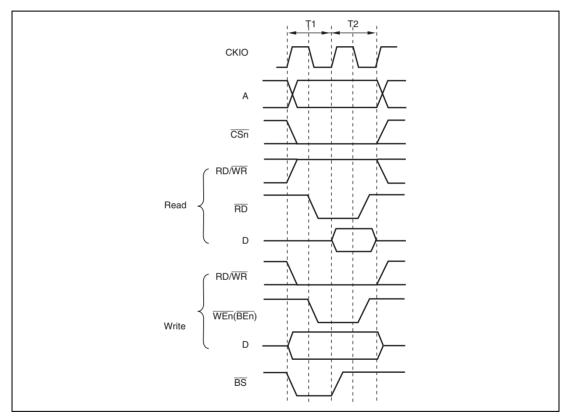

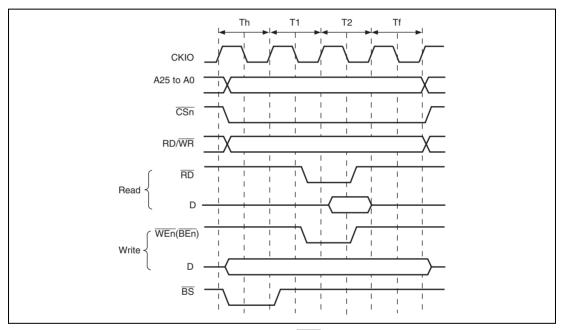

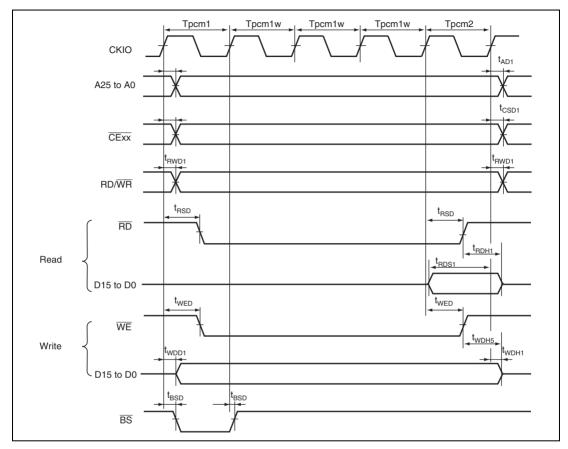

| Figure 7.3  | Normal Space Basic Access Timing (No-Wait Access)                            | 149 |

| Figure 7.4  | Consecutive Access to Normal Space (1): Bus Width = 16 bits, Longword Access |     |

|             | CSnWCR.WM = 0 (Access Wait = 0, Cycle Wait = 0)                              |     |

| Figure 7.5  | Consecutive Access to Normal Space (2): Bus Width = 16 bits, Longword Access |     |

|             | CSnWCR.WM = 1 (Access Wait = 0, Cycle Wait = 0)                              |     |

|             | Example of 32-Bit Data-Width SRAM Connection                                 |     |

| 0           | Example of 16-Bit Data-Width SRAM Connection                                 |     |

| _           | Example of 8-Bit Data-Width SRAM Connection                                  |     |

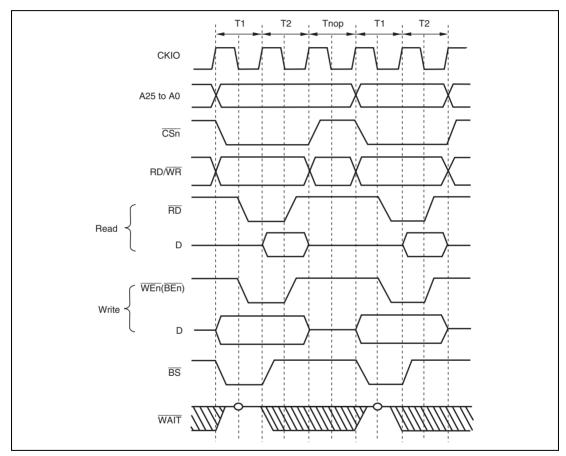

| _           | Wait Timing for Normal Space Access (Software Wait Only)                     | 154 |

| Figure 7.10 | Wait Cycle Timing for Normal Space Access                                    |     |

|             | (Wait cycle Insertion using WAIT)                                            |     |

| -           | Example of Timing when CSn Assertion Period is Extended                      |     |

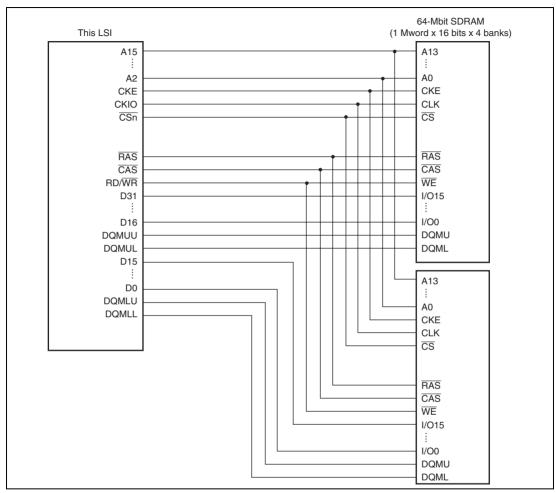

| _           | 2 Example of 32-Bit Data-Width SDRAM Connection                              |     |

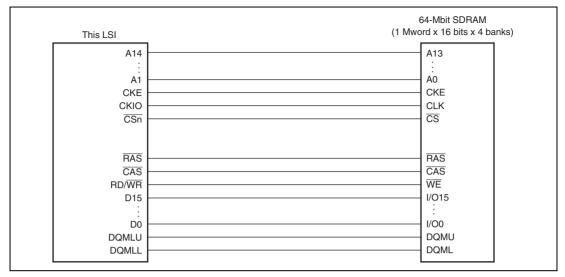

| Figure 7.13 | 3 Example of 16-Bit Data-Width SDRAM Connection                              | 159 |

| Figure 7.14 | Burst Read Basic Timing (Auto Precharge)                           | 1 /0 |

|-------------|--------------------------------------------------------------------|------|

| Figure 7.15 | Burst Read Wait Specification Timing (Auto Precharge)              | 171  |

| Figure 7.16 | Basic Timing for Single Read (Auto Precharge)                      | 172  |

| Figure 7.17 | Basic Timing for Burst Write (Auto Precharge)                      | 173  |

| Figure 7.18 | Basic Timing for Single Write (Auto-Precharge)                     | 174  |

| Figure 7.19 | Burst Read Timing (No Auto Precharge)                              | 176  |

| Figure 7.20 | Burst Read Timing (Bank Active, Same Row Address)                  | 177  |

| Figure 7.21 | Burst Read Timing (Bank Active, Different Row Addresses)           | 178  |

| Figure 7.22 | Single Write Timing (No Auto Precharge)                            | 179  |

| Figure 7.23 | Single Write Timing (Bank Active, Same Row Address)                | 180  |

| Figure 7.24 | Single Write Timing (Bank Active, Different Row Addresses)         | 181  |

| Figure 7.25 | Auto-Refreshing Timing                                             | 182  |

| Figure 7.26 | Self-Refreshing Timing                                             | 184  |

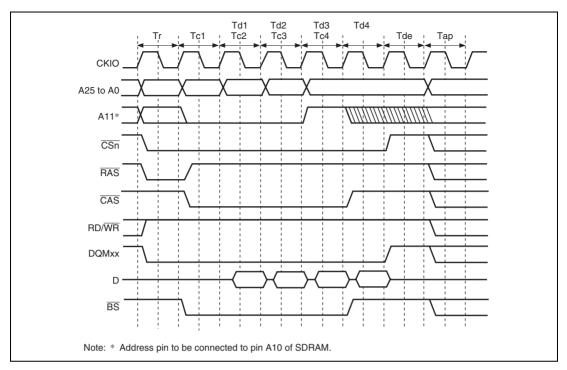

| Figure 7.27 | Write Timing for SDRAM Mode Register (Based on JEDEC)              | 186  |

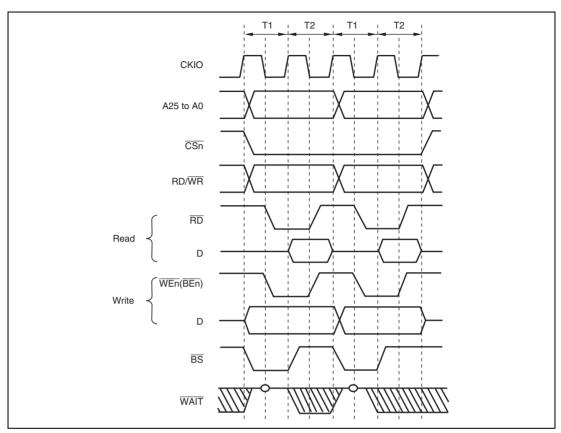

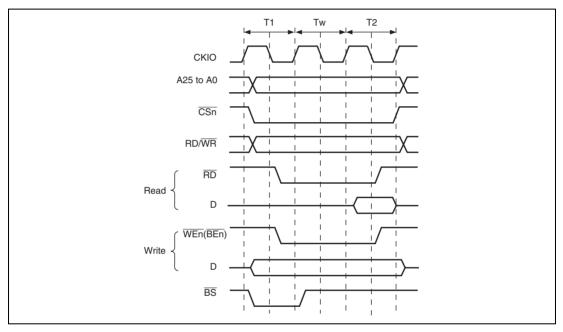

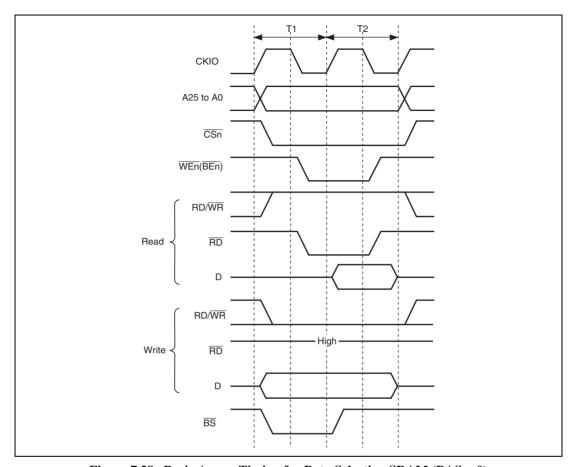

| Figure 7.28 | Basic Access Timing for Byte-Selection SRAM (BAS = 0)              | 187  |

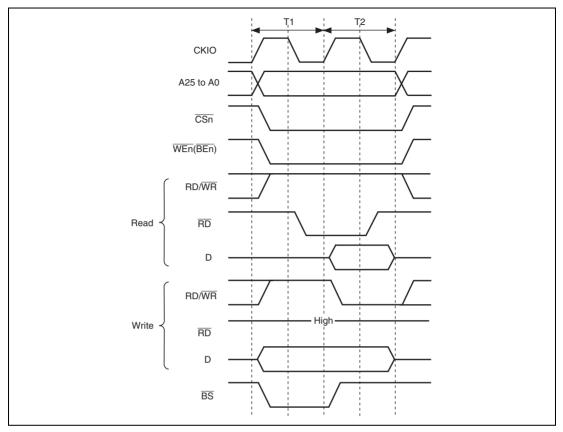

| Figure 7.29 | Basic Access Timing for Byte-Selection SRAM (BAS = 1)              | 188  |

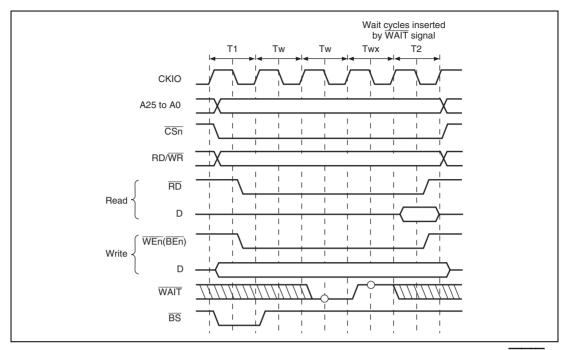

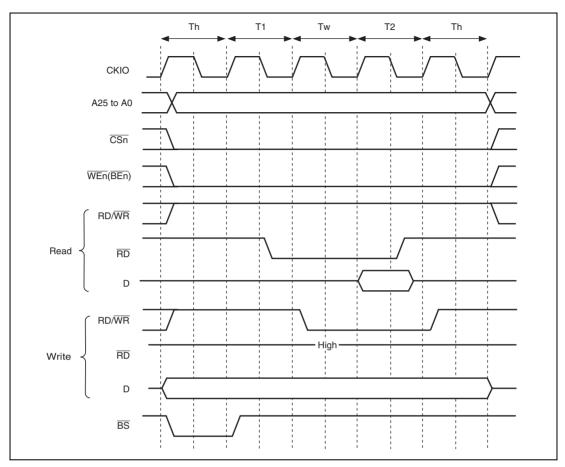

| Figure 7.30 | Wait Timing for Byte-Selection SRAM (BAS = 1) (Software Wait Only) | 189  |

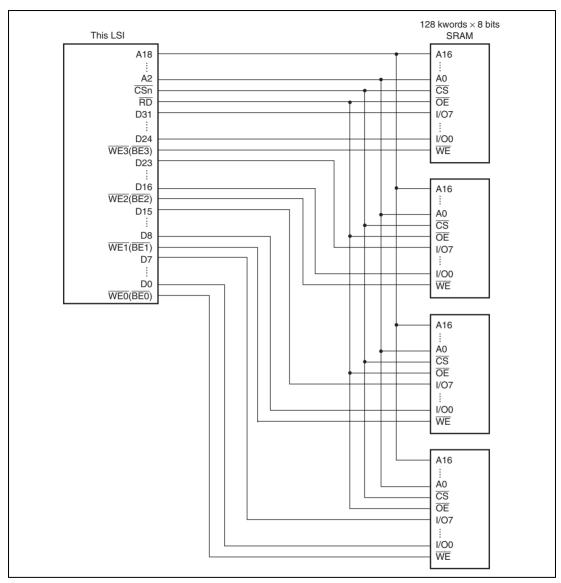

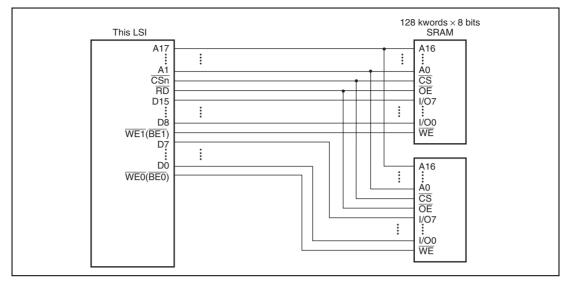

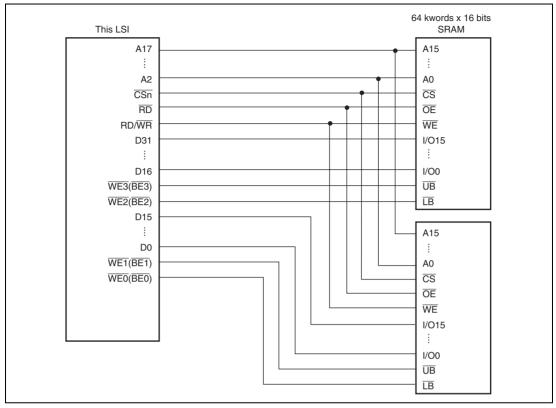

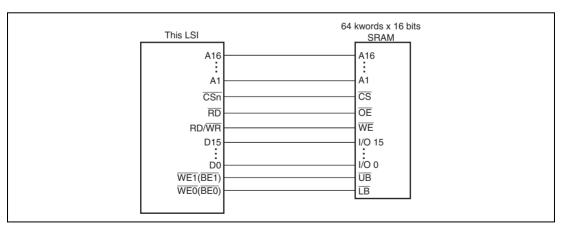

| Figure 7.31 | Example of Connection with 32-Bit Data-Width Byte-Selection SRAM   | 190  |

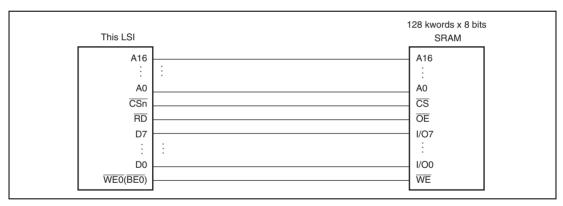

| Figure 7.32 | Example of Connection with 16-Bit Data-Width Byte-Selection SRAM   | 190  |

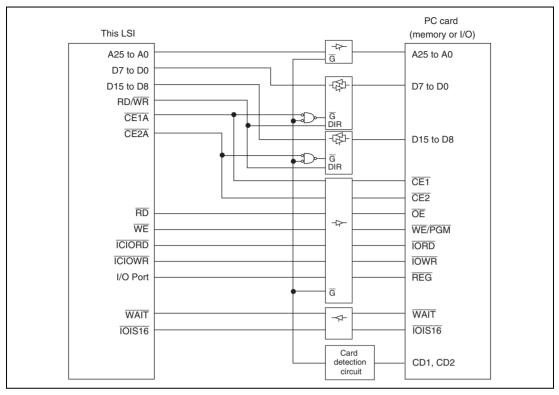

| Figure 7.33 | Example of PCMCIA Interface Connection                             | 192  |

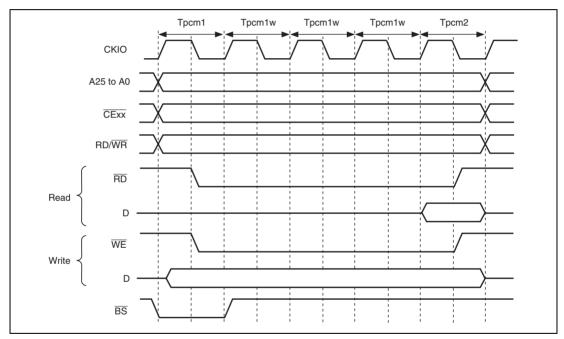

| Figure 7.34 | Basic Access Timing for PCMCIA Memory Card Interface               | 193  |

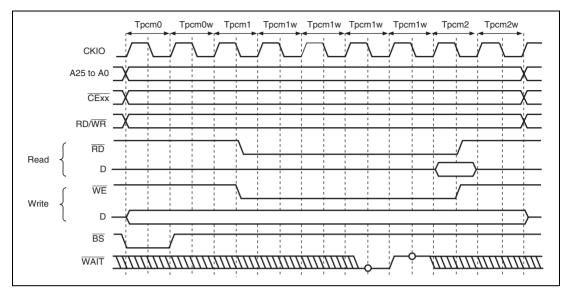

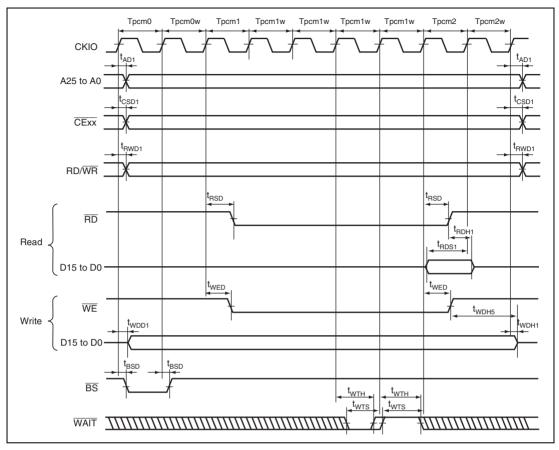

| Figure 7.35 | Wait Timing for PCMCIA Memory Card Interface                       |      |

|             | (TED[3:0] = B'0010, TEH[3:0] = B'0001, Software Wait = 1,          |      |

|             | Hardware Wait = 1)                                                 | 194  |

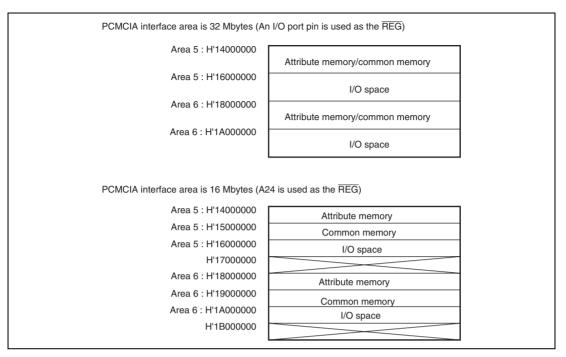

| Figure 7.36 | Example of PCMCIA Space Assignment (CS5BWCR.SA[1:0] = B'10,        |      |

|             | CS6BWCR.SA[1:0] = B'10)                                            |      |

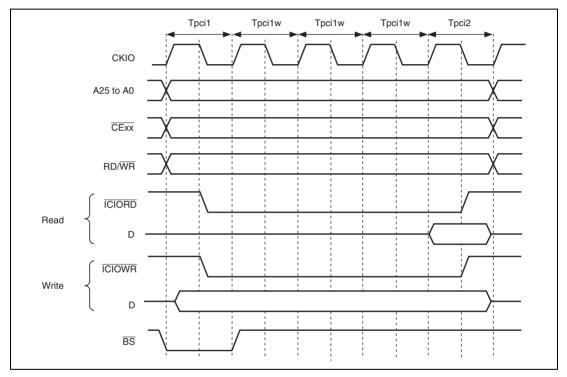

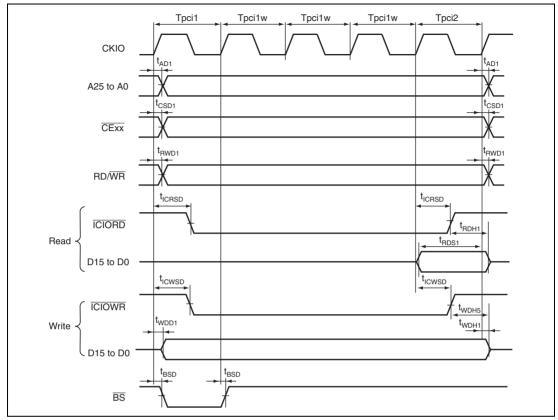

| Figure 7.37 | Basic Timing for PCMCIA I/O Card Interface                         | 196  |

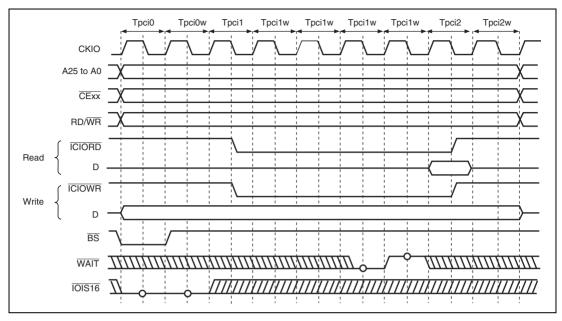

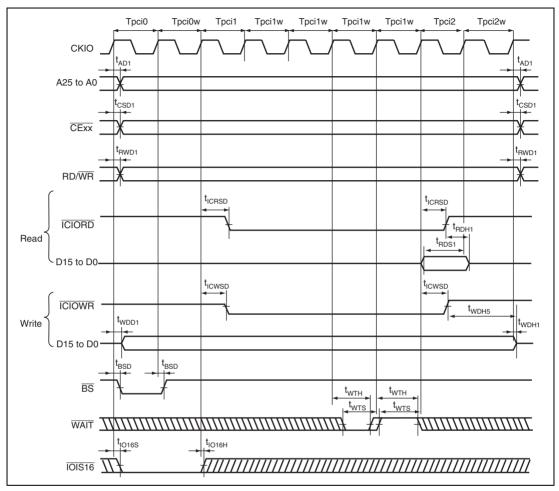

| Figure 7.38 | Wait Timing for PCMCIA I/O Card Interface (TED[3:0] = B'0010,      |      |

|             | TEH[3:0] = B'0001, Software Wait = 1, Hardware Wait = 1)           | 197  |

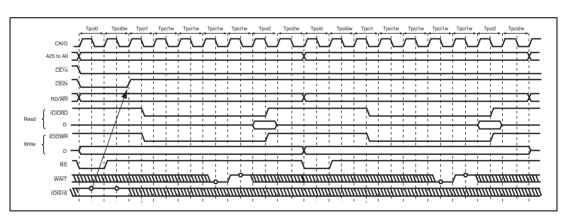

| Figure 7.39 | Timing for Dynamic Bus Sizing of PCMCIA I/O Card Interface         |      |

|             | (TED[3:0] = B'0010, TEH[3:0] = B'0001, Software Waits = 3)         | 197  |

| Section 8 C | Clock Pulse Generator (CPG)                                        |      |

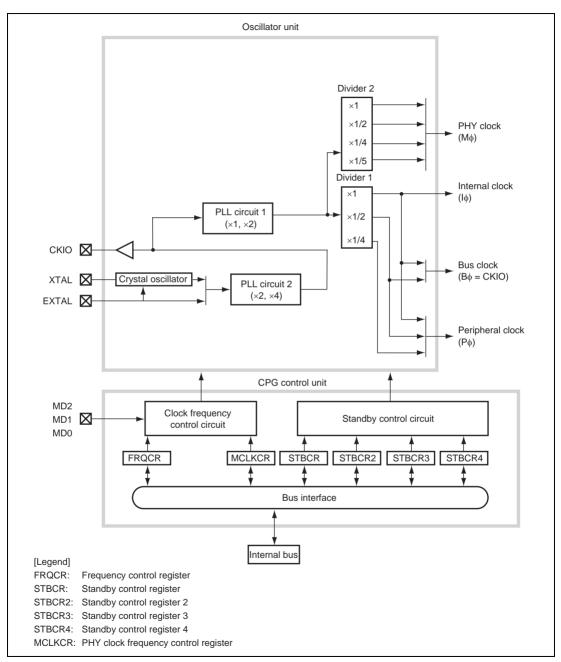

| Figure 8.1  | Block Diagram of CPG                                               | 202  |

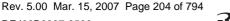

| Figure 8.2  | Note on Using a Crystal Resonator                                  | 213  |

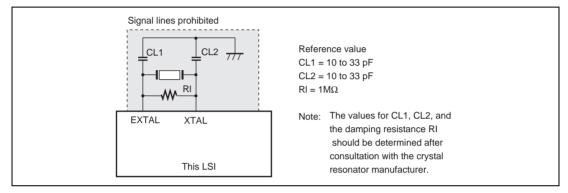

| -           | Note on Using a PLL Oscillator Circuit                             |      |

| Section 9 V | Vatchdog Timer (WDT)                                               |      |

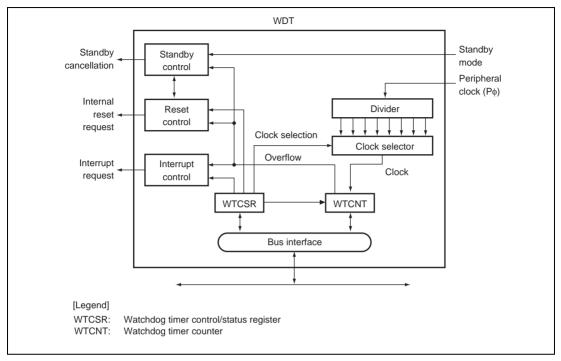

| Figure 9.1  | Block Diagram of WDT                                               | 216  |

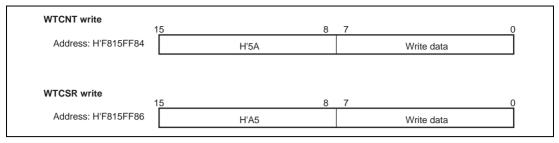

| Figure 9.2  | Writing to WTCNT and WTCSR                                         | 220  |

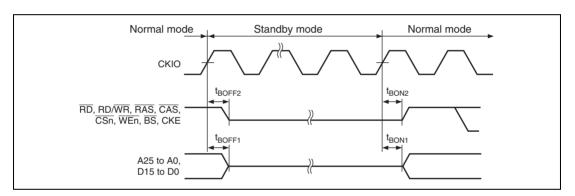

| Section 10 Power-Down Modes                                                             |

|-----------------------------------------------------------------------------------------|

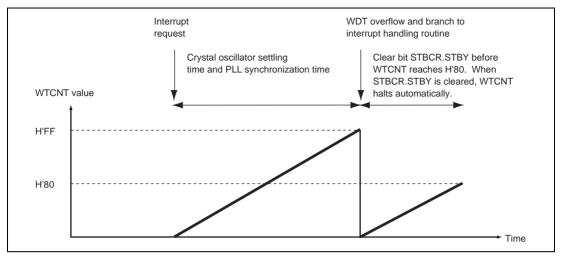

| Figure 10.1 Canceling Standby Mode with STBY Bit in STBCR                               |

| Section 11 Ethernet Controller (EtherC)                                                 |

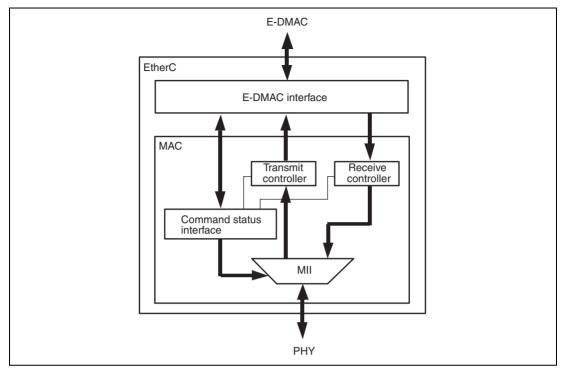

| Figure 11.1 Configuration of EtherC234                                                  |

| Figure 11.2 EtherC Transmitter State Transitions                                        |

| Figure 11.3 EtherC Receiver State Transmissions                                         |

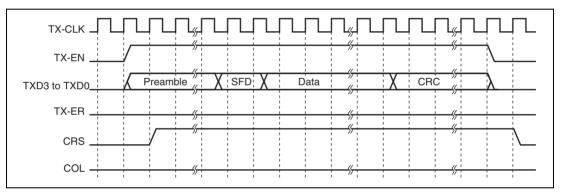

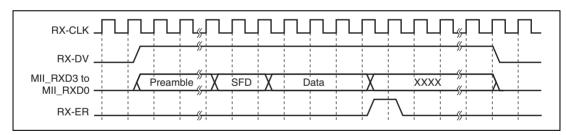

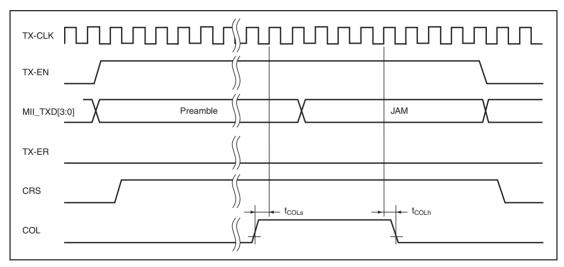

| Figure 11.4 (1) MII Frame Transmit Timing (Normal Transmission)256                      |

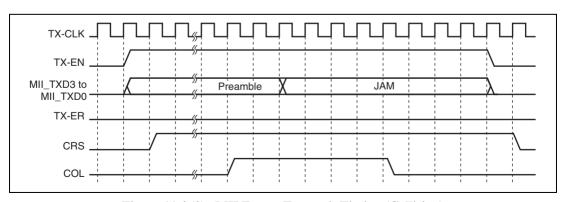

| Figure 11.4 (2) MII Frame Transmit Timing (Collision)                                   |

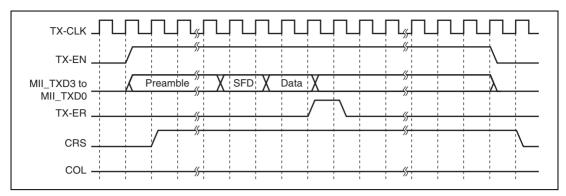

| Figure 11.4 (3) MII Frame Transmit Timing (Transmit Error)                              |

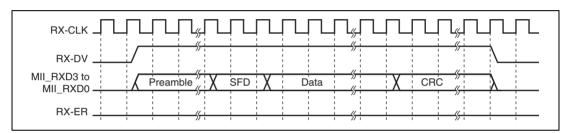

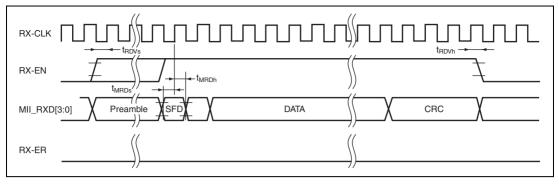

| Figure 11.4 (4) MII Frame Receive Timing (Normal Reception)25                           |

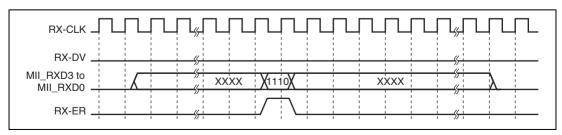

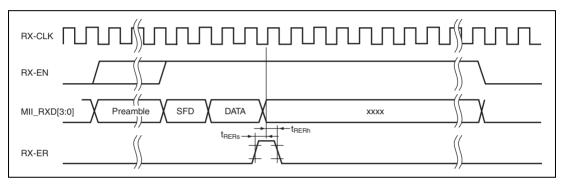

| Figure 11.4 (5) MII Frame Receive Timing (Reception Error (1))25                        |

| Figure 11.4 (6) MII Fame Receive Timing (Reception Error (2))25                         |

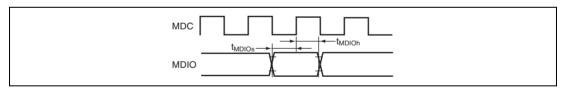

| Figure 11.5 MII Management Frame Format                                                 |

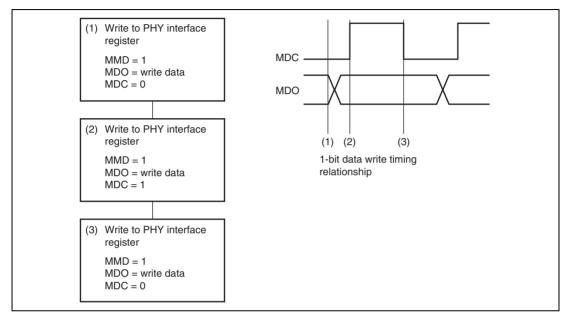

| Figure 11.6 (1) 1-Bit Data Write Flowchart                                              |

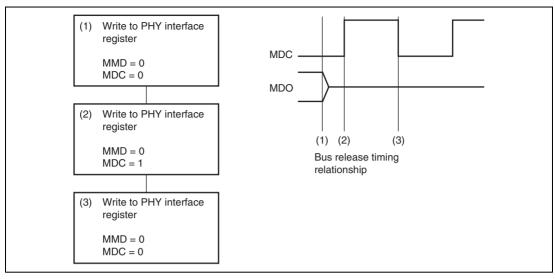

| Figure 11.6 (2) Bus Release Flowchart (TA in Read in Figure 11.5)260                    |

| Figure 11.6 (3) 1-Bit Data Read Flowchart                                               |

| Figure 11.6 (4) Independent Bus Release Flowchart (IDLE in Write in Figure 11.5)26      |

| Figure 11.7 Changing IPG and Transmission Efficiency                                    |

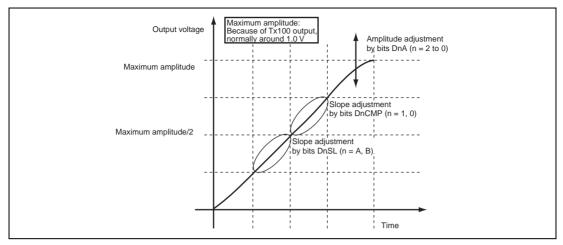

| Figure 11.8 Example of Connection to DP83846AVHG263                                     |

| Section 12 Ethernet Controller Direct Memory Access Controller                          |

| (E-DMAC)                                                                                |

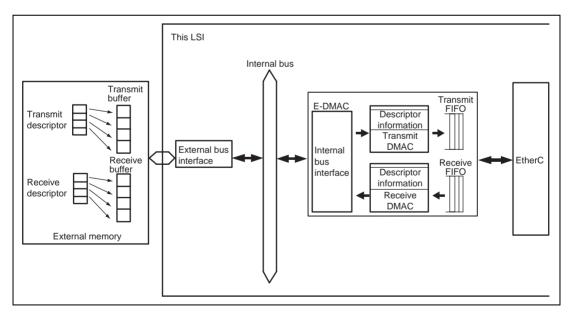

| Figure 12.1 Configuration of E-DMAC, and Descriptors and Buffers265                     |

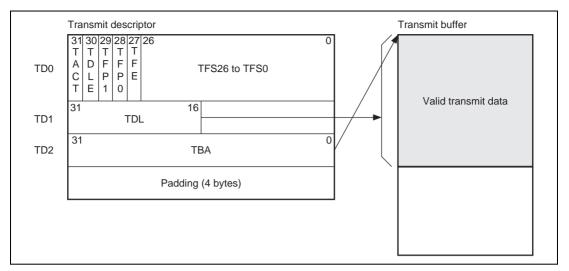

| Figure 12.2 Relationship between Transmit Descriptor and Transmit Buffer290             |

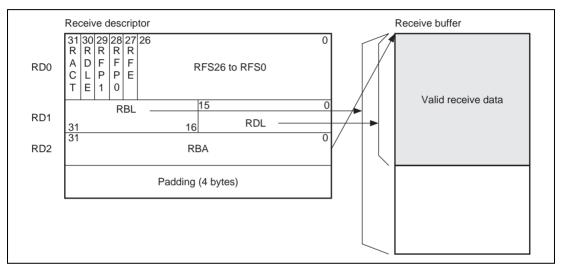

| Figure 12.3 Relationship between Receive Descriptor and Receive Buffer294               |

| Figure 12.4 Sample Transmission Flowchart                                               |

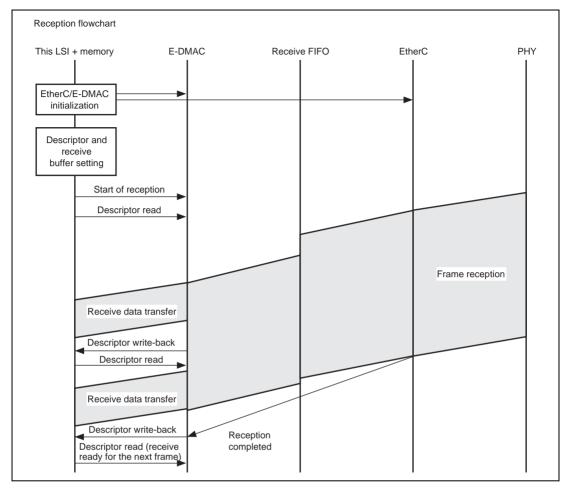

| Figure 12.5 Sample Reception Flowchart                                                  |

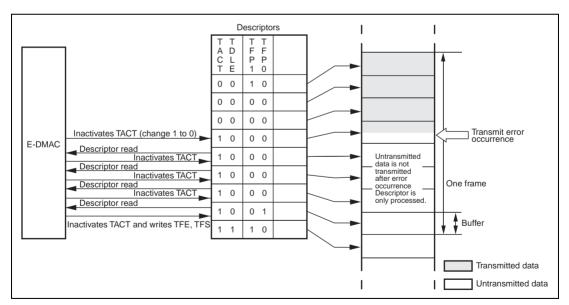

| Figure 12.6 E-DMAC Operation after Transmit Error                                       |

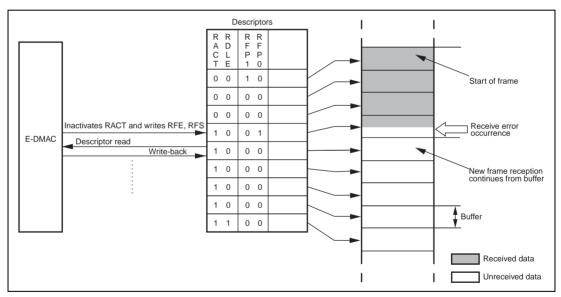

| Figure 12.7 E-DMAC Operation after Receive Error                                        |

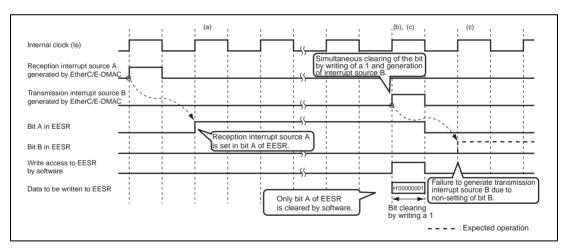

| Figure 12.8 Timing of the Case where Setting of the Interrupt Source Bit in EESR        |

| by the E-DMAC Fails                                                                     |

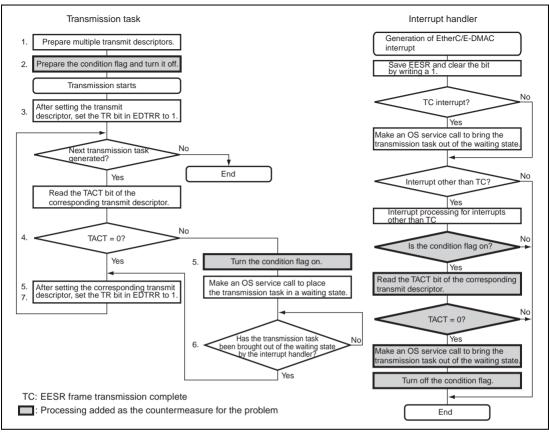

| Figure 12.9 Countermeasure by Monitoring the Transmit Descriptor in Processing of       |

| Interrupts Other than the Frame Transmit Complete (TC) Interrupt310                     |

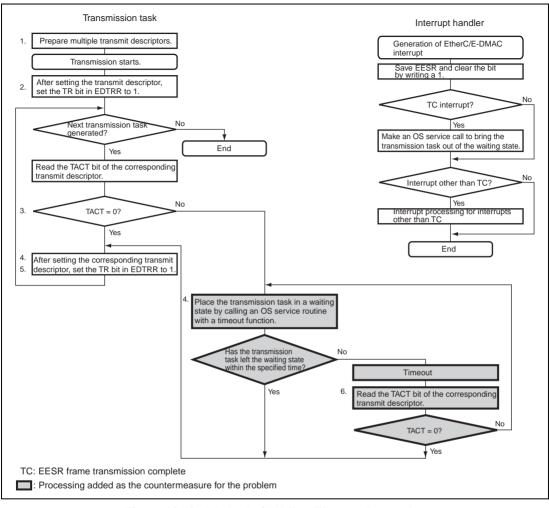

| Figure 12.10 Method of Adding Timeout Processing312                                     |

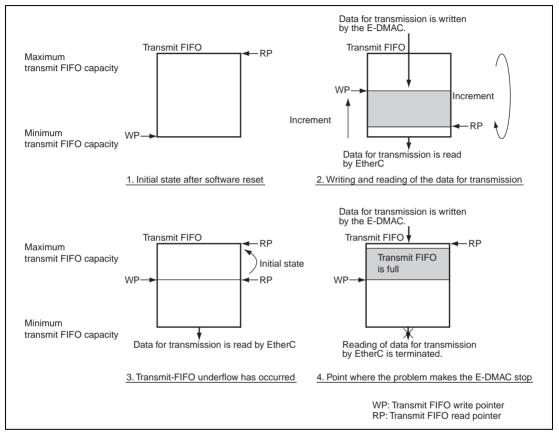

| Figure 12.11 Operation when E-DMAC Stops and the Transmit FIFO314                       |

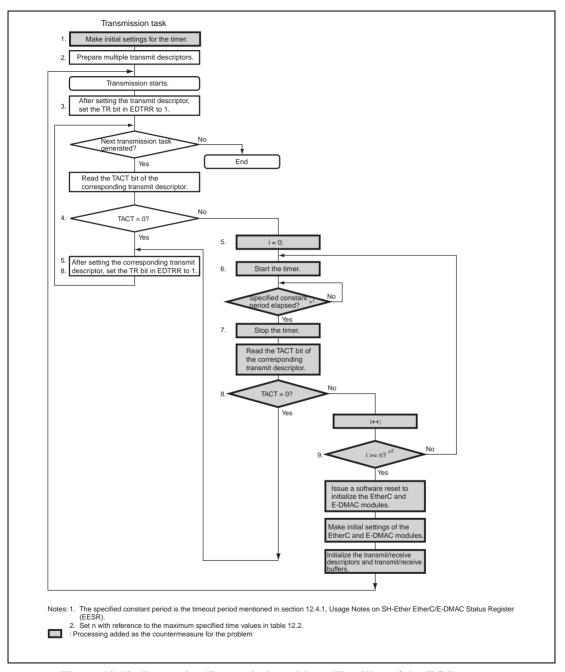

| Figure 12.12 Processing Transmission without Handling of the TC Interrupt31             |

| Figure 12.13 Countermeasure for the Case with TC Interrupt-Driven Software: Addition of |

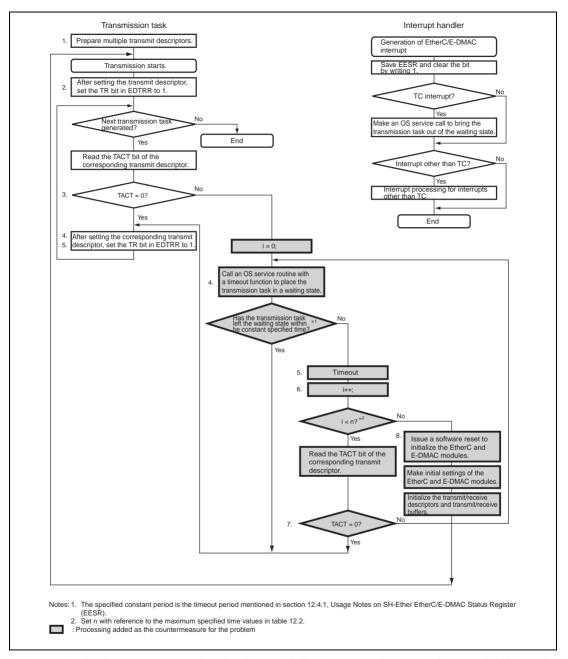

| Timeout Processing within the Limit Imposed by the Maximum Specified Time. 320          |

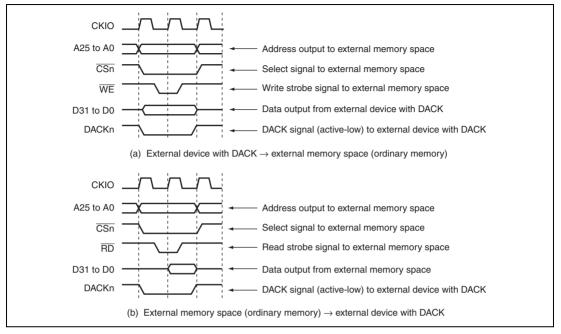

| Figure 13.5 Data Flow of Dual Address Mode                                                                                                                                                                              |               | rect Memory Access Controller (DMAC)                                |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------|-----|

| Figure 13.3         Round-Robin Mode                                                                                                                                                                                    | Figure 13.1 B | Block Diagram of DMAC                                               | 324 |

| Figure 13.4 Changes in Channel Priority in Round-Robin Mode                                                                                                                                                             | Figure 13.2   | DMA Transfer Flowchart                                              | 338 |

| Figure 13.5 Data Flow of Dual Address Mode                                                                                                                                                                              | Figure 13.3 R | Round-Robin Mode                                                    | 342 |

| Figure 13.6 Example of DMA Transfer Timing in Dual Mode (Source: Ordinary Memory, Destination: Ordinary Memory)                                                                                                         | Figure 13.4 C | Changes in Channel Priority in Round-Robin Mode                     | 343 |

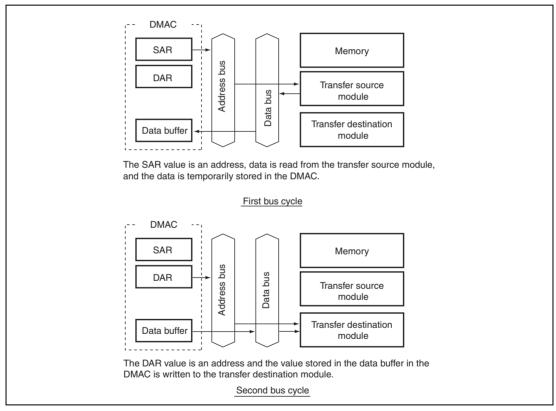

| (Source: Ordinary Memory, Destination: Ordinary Memory)                                                                                                                                                                 | Figure 13.5 D | Oata Flow of Dual Address Mode                                      | 345 |

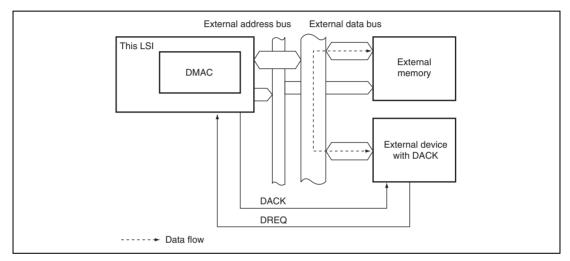

| Figure 13.7 Data Flow in Single Address Mode                                                                                                                                                                            | Figure 13.6 E | Example of DMA Transfer Timing in Dual Mode                         |     |

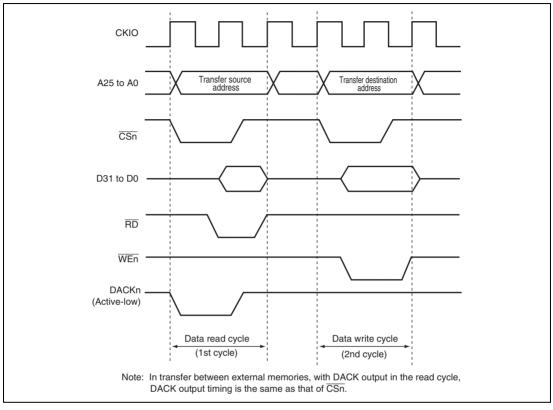

| Figure 13.8 Example of DMA Transfer Timing in Single Address Mode                                                                                                                                                       | (             | (Source: Ordinary Memory, Destination: Ordinary Memory)             | 346 |

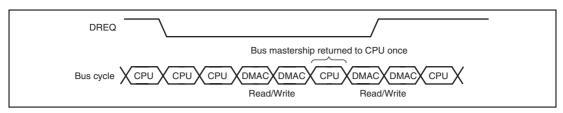

| Figure 13.9 DMA Transfer Example in Cycle-Steal Normal Mode (Dual Address, DREQ Low Level Detection)                                                                                                                    | Figure 13.7 D | Oata Flow in Single Address Mode                                    | 347 |

| (Dual Address, DREQ Low Level Detection)                                                                                                                                                                                | Figure 13.8 E | Example of DMA Transfer Timing in Single Address Mode               | 348 |

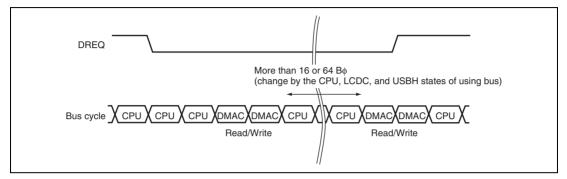

| Figure 13.10 Example of DMA Transfer in Cycle Steal Intermittent Mode (Dual Address, DREQ Low Level Detection)                                                                                                          | Figure 13.9 D | DMA Transfer Example in Cycle-Steal Normal Mode                     |     |

| (Dual Address, DREQ Low Level Detection)                                                                                                                                                                                | (             | (Dual Address, DREQ Low Level Detection)                            | 349 |

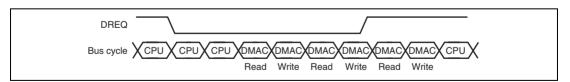

| Figure 13.11 DMA Transfer Example in Burst Mode (Dual Address, DREQ Low Level Detection)                                                                                                                                | Figure 13.10  | Example of DMA Transfer in Cycle Steal Intermittent Mode            |     |

| (Dual Address, DREQ Low Level Detection)                                                                                                                                                                                |               | (Dual Address, DREQ Low Level Detection)                            | 350 |

| Figure 13.12 Bus State when Multiple Channels are Operating                                                                                                                                                             | Figure 13.11  | DMA Transfer Example in Burst Mode                                  |     |

| Figure 13.13 Example of DREQ Input Detection in Cycle Steal Mode Edge Detection                                                                                                                                         |               | (Dual Address, DREQ Low Level Detection)                            | 350 |

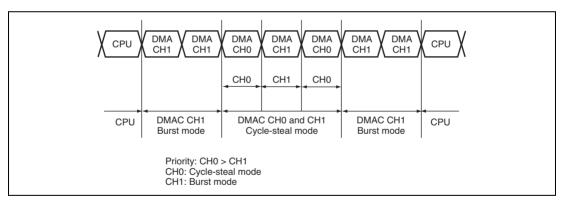

| Figure 13.14 Example of DREQ Input Detection in Cycle Steal Mode Level Detection                                                                                                                                        | Figure 13.12  | Bus State when Multiple Channels are Operating                      | 352 |

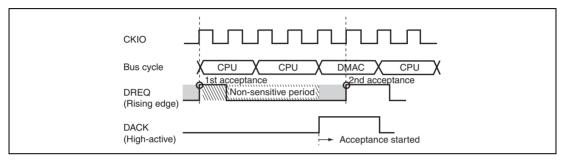

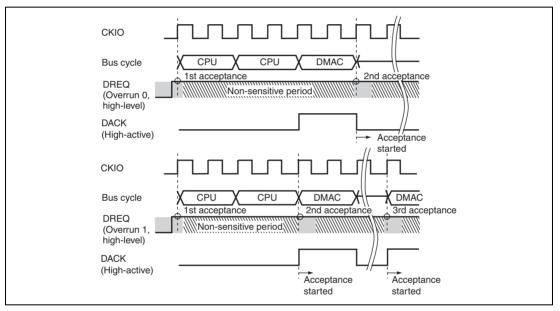

| Figure 13.15 Example of DREQ Input Detection in Burst Mode Edge Detection                                                                                                                                               | Figure 13.13  | Example of DREQ Input Detection in Cycle Steal Mode Edge Detection  | 353 |

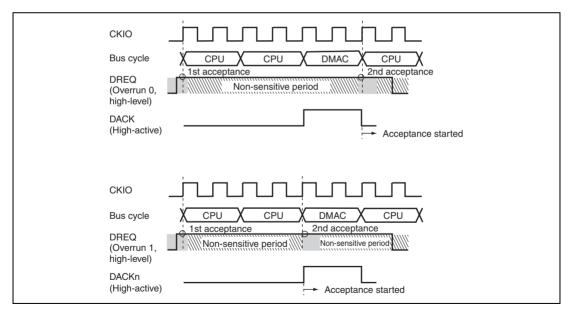

| Figure 13.16 Example of DREQ Input Detection in Burst Mode Level Detection                                                                                                                                              | Figure 13.14  | Example of DREQ Input Detection in Cycle Steal Mode Level Detection | 353 |

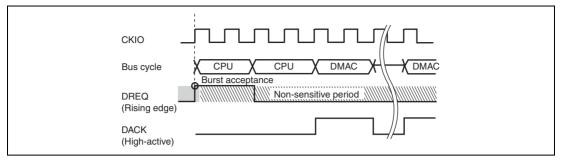

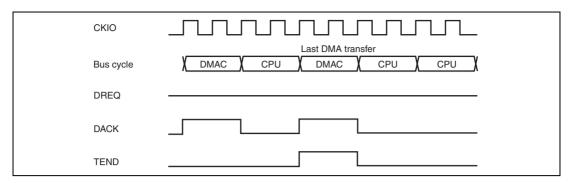

| Figure 13.17 Example of DMA Transfer End in Cycle Steal Mode Level Detection                                                                                                                                            | Figure 13.15  | Example of DREQ Input Detection in Burst Mode Edge Detection        | 354 |

| Figure 13.18 Example of BSC Ordinary Memory Access (No Wait, Idle Cycle 1, Longword Access to 16-Bit Device)                                                                                                            | Figure 13.16  | Example of DREQ Input Detection in Burst Mode Level Detection       | 354 |

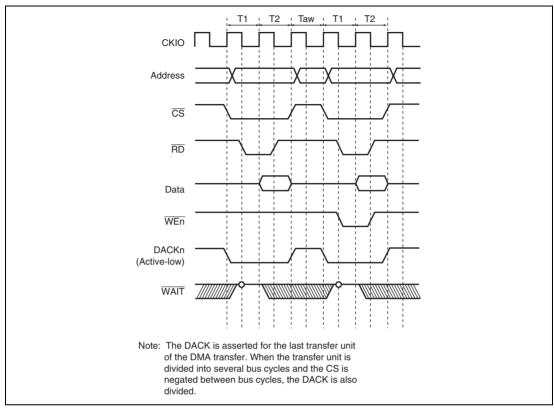

| (No Wait, Idle Cycle 1, Longword Access to 16-Bit Device)                                                                                                                                                               | Figure 13.17  | Example of DMA Transfer End in Cycle Steal Mode Level Detection     | 355 |

| Figure 13.19 Example of DREQ Input Detection in Cycle Steal Mode Edge Detection When DACK is Divided to 4 by Idle Cycles                                                                                                | Figure 13.18  | Example of BSC Ordinary Memory Access                               |     |

| When DACK is Divided to 4 by Idle Cycles                                                                                                                                                                                |               | (No Wait, Idle Cycle 1, Longword Access to 16-Bit Device)           | 356 |

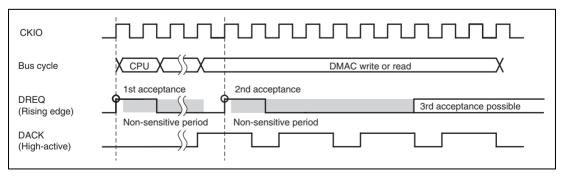

| Figure 13.20 Example of DREQ Input Detection in Cycle Steal Mode Edge Detection When DACK is Divided to 2 by Idle Cycles                                                                                                | Figure 13.19  |                                                                     |     |

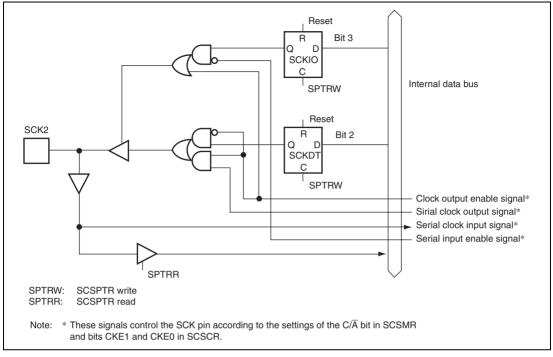

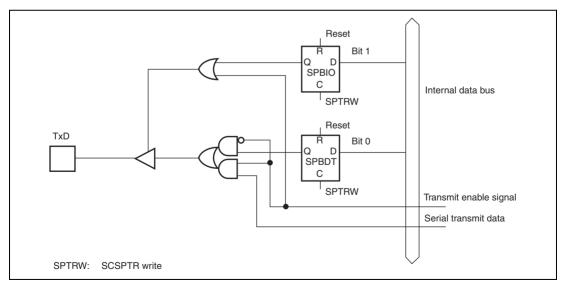

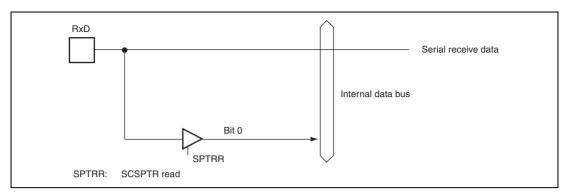

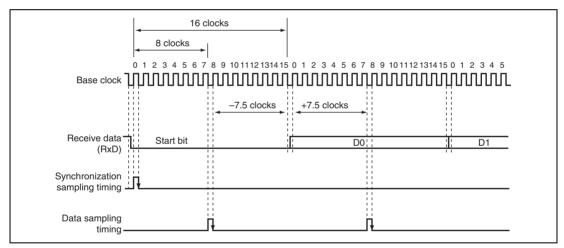

| When DACK is Divided to 2 by Idle Cycles                                                                                                                                                                                |               | When DACK is Divided to 4 by Idle Cycles                            | 358 |